基于PCI总线的高速CCD图像存储系统设计

1引言

侦察与监视在军事斗争中的地位举足轻重。在各种侦察/监视技术中,航空侦察占有重要的地位,可见光侦察是一种重要的侦察形式,无人侦察机显示出了广阔的发展前景,现代科学技术的发展为现代航空侦察与监视技术带来了新的发展契机。

航空侦察一个主要的途径就是利用高性能高速摄像机进行航空拍照,采集各种图像信息。然而,数字化的侦察图像分辨率高、信息量大,使后续的处理、传输、存储等过程的实现变得极为困难,从而给机载图像/视频系统的设计与实现带来了巨大的挑战。为了解决这些问题,本文基于某型高速相机,利用低成本FPGA,构建了一个高性能的图像采集存储系统,完成对高分辨率、高帧率侦察图像的采集和存储。

2某型高速相机简介

系统选择的高速相机是一款高分辨率、高速度线扫数字相机,其图像传感器采用先进的CCD(Charge-CoupledDevice)图像传感器,采用了世界尖端水平的高灵敏度扫描成像技术——高速率的TDI(TimeDelayandIntegration)技术、多重曝光技术并加强蓝色响应,从而使该型相机可提供比单输出线扫相机更好的灵敏度特性,总的数据传输率可高达200MB/s。

相机接口主要包括后面板上的六个接口:其中四个为数据输出接口,每个接口包括16位数据信号,1位数据同步信号,1位同步时钟信号,信号的电平输出格式为LVDS电平格式;另外两个接口分别为控制信号接口和电源接口。在控制信号的作用下,相机同步输出包含同步时钟信号(STROBE)和水平同步信号(LVAL)在内的8×8bit标准的灰度图像数据,图像分辨率可选择为4096×30`72(本系统采用分辨率)和2048×3072。

相机控制接口信号中,行触发信号(EXSYNC)至关重要。它负责图像数据的触发输出,行触发信号的上升沿触发数据并指示数据有效。相机触发要求此信号存在下降沿,最小触发频率为300HZ。

3系统硬件设计及工作原理

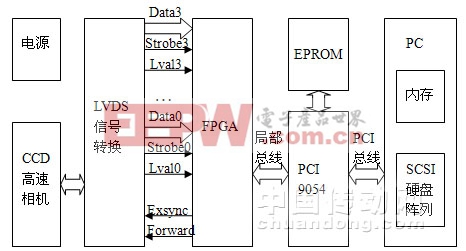

本设计硬件系统主要包括电平转换,数据接收预处理和数据采集存储三个部分。图1为系统硬件原理框图。在总线结构上,系统采用了满足高速数据传输的PCI总线结构,PCI9054是PLX公司推出的一种32位33MHz的PCI总线主控I/O加速器,它采用多种先进技术,使复杂的PCI接口应用设计变得相对简单。

从资源和成本方面考虑,FPGA选用Altera公司的低成本Cyclone系列芯片-EP1C6Q240C8。存储介质则选用SCSI磁盘阵列,它能满足高速、大数据量的存储。

图1系统原理框图

系统工作原理:

系统上电,首先完成一系列初始化工作:PC通过底层驱动配置PCI9054的寄存器,使之处于正常工作模式(C模式)[2];FPGA上电,配置用户电路(此时,FPGA内部逻辑和PCI9054都处于等待状态)。

PC应用程序启动后,向PCI9054发送数据传输指令,PCI9054收到数据传输指令,通过LOCALBUS通知FPGA开始工作:FPGA产生行触发信号(EXSYNC),触发相机进行拍照、传输数据。然后,PCI9054进入工作状态,开始采集数据,并将数据存储到磁盘阵列。FPGA内部逻辑和PC应用程序通过行计数判断一帧图像传输完毕,相继进入等待状态。但是,PC应用程序在接收完一帧图像,进入等待状态后,延续一定时间,会自动触发下一个数据传输指令通知FPGA开始下一帧图像传输。

电平格式转换

PCI9054芯片电平格式为3.3VLVTTL格式,相机输出信号的电平格式为LVDS格式,基于系统总体需要,有必要在进行图像预处理前将LVDS相机输出信号转换成LVTTL格式电平。

数据接收预处理

FPGA完成图像预处理功能。FPGA是以并行运算为主导的芯片,处理速度更快。数据预处理过程包括:数据缓冲、位并转换。

数据缓冲[3]:相机利用4个通道输出图像数据,每个端口的数据传输以本端口时钟为参考,传输过程中由于各种差异如传输电缆的长度不同,使得各个端口的时钟信号产生相对的相位漂移,从而使四个端口数据输出不完全同步,这不利于图像数据的同步采集。为消除数据异步,FPGA内部设计了由4个FIFO组成的数据缓冲器组。每个端口的有效数据宽度为16bit,传送一行4096个数据需用512个时钟周期,因此FIFO深度设为512个字。相机送来的4个LVAL信号为各对应通道写使能信号,4个STROBE信号作为对应通道写时钟。FIFO输出端采用系统时钟(15MHz)作为统一的数据同步时钟,并设计一个读请求信号,当FIFO半满时读取数据,经过缓存的数据以与系统时钟同步的64bit宽度格式输出。

位并转换:PCI9054芯片LOCAL端的有效数据位数有两种选择:8bit和32bit(可更改9054寄存器设置,为了保证数据采集速度,本系统设置为32bit)。但是相机的输出数据通过缓冲之后仍然为64bit,为了满足PCI9054数据采集位数要求,

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于Linux平台的天气雷达高速数据采集系统设计(03-13)

- 基于DSP与PC机的PCI总线高速数据传输 (07-08)