T-MMB系统中LDPC码译码器的FPGA设计与实现

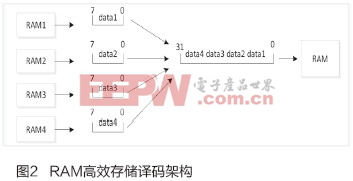

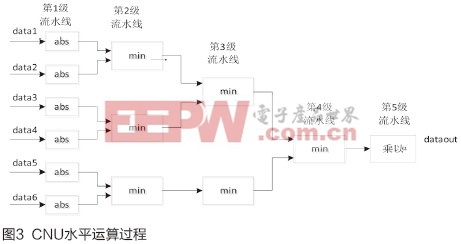

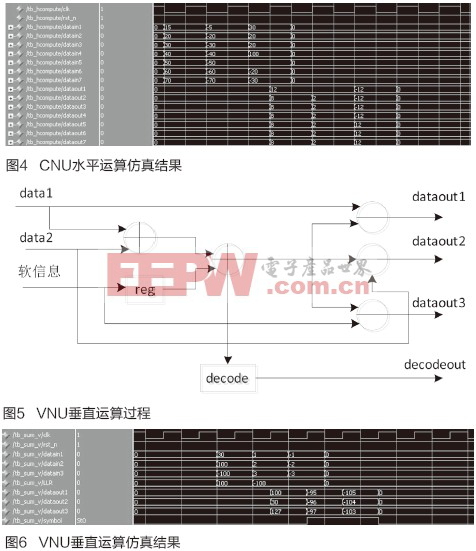

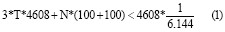

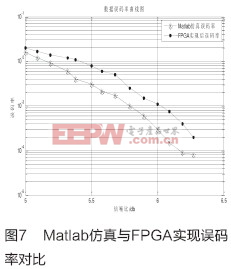

系列的FPGA进行实现,采取自带块RAM的存储方式,RAM容量为18Kb。在实现时,将块RAM例化为宽度32bit深度155的双口块RAM,深度0~71上存放校验节点信息,深度80~151上存放变量节点信息。因为校验节点与变量节点同时处理的多个消息必须同时读出或写入存储器中[10]。为保证同步,本文采取的做法是将偏移量相同的子矩阵对应的校验节点信息或变量节点信息存储到同一块RAM中。由于Xilinx的块RAM最大位宽为32bit,所以最多有4个子矩阵对应的信息可以存储到同一块RAM中。存储方式如图2所示。 本文设计的高效存储方式偏移量最多为71,同一种信息对应的子矩阵为224,与传统存储方式相比可以节省75%的RAM资源。这种存储方式不仅减少了块RAM资源的浪费,也减少了译码器实现所需的存储资源数量。表2对比了传统存储方式与改进后的RAM存储方式资源的占用情况。 主要模块的硬件实现 针对本文提出的高效存储译码架构,本文在实际的FPGA硬件平台上进行了译码器验证。下面列举了主要功能模块的硬件设计,其中译码器的各模块均采用了多级流水线技术。 校验节点处理单元(CNU) CNU总体被划分为5级流水线,其结构如图3所示。乘法电路采用减法及移位操作来代替,从而简化计算电路。这种运行方式运行在较高的时钟频率下,该模块的最高时钟频率可以达到171.73MHz。图4表示了水平运算的FPGA仿真结果。 变量节点处理单元(VNU) 在LDPC码的迭代译码过程中,变量节点处理单元以加减运算为主,数据以补码形式表示有利于简化操作[10],本文实现的VNU流水线结构如图5所示。图6表示垂直运算的FPGA运算结果,该模块的时钟频率最高可以达到321.62MHz。 实现结果 在T-MMB系统中,OFDM进行逆快速傅里叶变换的速率为2.048M符号/s。接收端在接收该信号后进行8PSK软解调,因此软解调模块的工作速率需要达到3×2.048MHz即6.144MHz才能满足系统时序要求。本次设计中软解调模块的时钟频率可以达到216.16MHz,满足系统要求。 译码器接收信息的速率为6.144MHz,需要能对每一组输入的软信息进行正确译码,保证在下一组软信息开始译码的时候上一次译码已经结束。则译码器工作频率要满足公式(1)要求。 T为译码器的工作周期,N为规定的迭代次数,100+100是为了保证系统性能防止溢出将水平运算次数与垂直运算次数扩大为100。由公式(1)可得到译码工作频率至少为30MHz,而本文实现译码器的时钟频率可以达到86.38MHz,可以满足系统对译码器时钟频率的要求。 本文首先进行了Matlab浮点运算仿真,之后对译码器进行硬件实现。将Matlab中的浮点运算译码结果与8比特量化后经FPGA实现的译码结果进行对比,对比结果见图7。 由于FPGA处理定点数据,量化后译码性能与浮点数运算译码性能有一定的差距,但该性能在可接受的范围内,能够满足系统对译码器译码性能的要求。 结束语 本文利用QC-LDPC码的循环结构,采用部分并行结构设计实现了一种高效存储的译码器结构,将偏移量相同的子矩阵对应的校验节点信息或变量节点信息存储在相同的块RAM中。该方法能够有效减少QC-LDPC码译码器对BRAM资源的需求。基于Xilinx公司Vertex-4系列FPGA的实验结果表明,本文提出的存储方法与传统的存储方式相比可以节约75%的BRAM资源,实验还表明采用该方法得到的QC-LDPC码译码器能够实现较高的系统时钟频率,因而能够达到较大的译码吞吐量。 参考文献: ?

? ?

? ?

? ?

?

????????  ?

? ?

?

[1] 新一代地面移动多媒体广播系统(T-MMB)简介[J].数字通信世界,2006,(11):44-45

[2] 尹航,胡志强,肖如吾.移动多媒体广播系统中LDPC编码器的设计与实现[J].中国传媒大学学报自然科学版,2009,16,(4):78-84

[3] Gallager R G. Low-density Parity-check Codes[J].IRE Transactions on Information Theory, 1962,2,(8):21-28

[4] MacKay D J C, Cavendish L, Cambridge U. Good Error-correcting Codes Based on Very sparse matrices[C].Proc. IEEE International Symposium on Information Theory.1997:113.

[5] 徐欢,雷菁,文磊.准循环LDPC码低存储量译码器设计与实现[J].重庆邮电大学学报(自然科学版),2010,22(6):771-774.

[6] Fossorier M P C, Mihaljevic M, Imai H. Reduced complexity iterative decoding of low density parity check codes based on belief propagation[J].IEEE Transactions on Communications,1999,47(5):673-680.

[7] 何庆涛,周正,葛建华.准循环LDPC码译码器的FPGA实现[J].空间电子技术,2009,1:40-102.

[8] 乔华,管武,董明科,等.LDPC码高速译码器的设计与实现[J].北京大学学报(自然科学版),2007,2(2):1-6.

[9] 袁瑞佳,白宝明.基于FPGA的部分并行QC-LDPC译码器高效存储方法[J].通信学报,2012,33(11):165-170.

[10] 张仲明,许拔,杨军,等.800Mbps准循环LDPC码译码器的FPGA实现[J].信号处理,2010,26(2):255-261.

- 非规则LDPC码译码改进算法及其DSP实现(10-13)

- 一种基于FPGA的QC_LDPC码的译码器设计(05-13)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)