基于DSP 内嵌ECAN模块的总线接口设计

0 引言

CAN 总线以其可靠、实时、低成本优势已在汽车、机械等工业控制领域广泛应用。TMS320F2812是TI公司最具代表性的低成本、低功耗和高性能的定点DSP芯片,具有强大的事件管理能力和嵌入式控制能力。其内嵌的增强型CAN 总线控制器(ECAN)模块,完全兼容CAN 2.0B 协议,邮箱数量增加至32 个,并增加了时间戳、消息过滤和超时发送功能,提高了应用CAN通信的灵活性。

ADM3053是ADI公司2011年推出一款集成信号和电源隔离功能的CAN 收发器。本文采用集成ECAN 模块的TMS320F2812 和ADM3053 来设计CAN 节点。该设计将内嵌ECAN模块的DSP作为节点主控制器,同时采用ADM3053芯片有效替代了传统CAN收发器、信号隔离、供电隔离三部分电路,有效实现了模块小型化、低功耗、低成本。

本接口模块能够实现正常的CAN通信,通信控制更加灵活。采用CAN通信监控卡和专用示波器CANScope对该接口的数据包、电平特性、眼图进行分析,结果显示信号品质良好。

1 硬件设计

1.1 硬件系统设计

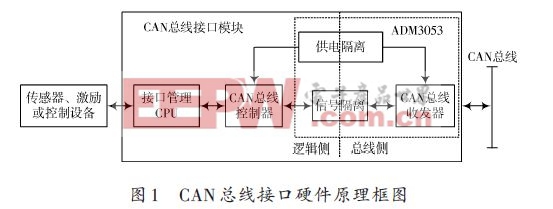

典型的工业控制中CAN总线接口模块硬件原理框图如图1所示,它由智能处理器、CAN协议控制器、信号隔离、收发器及供电隔离组成。智能处理器负责总线数据收发,CAN协议数据的解析和管理,响应上位机命令并反馈接口健康状态;CAN 总线控制器功能是实现数据链路层功能,包括位时序逻辑、错误管理逻辑、验收滤波器、收发缓冲管理等;CAN总线收发器功能是实现物理层功能,主要是收发信号与总线差分电平的相互转换;隔离电路包含信号隔离和电源隔离两部分,实现控制器与收发器之间的完全电气隔离。

传统的CAN总线接口电路是由采用独立的接口管理CPU、CAN控制器、收发器及隔离电路搭建,这种方法占用板面积大、接口逻辑复杂、成本高。本设计应用了ADI 公司最新发布的ADM3053 芯片,该芯片集成了CAN 收发器、信号隔离及供电隔离三部分功能,见图1中虚线方框部分。应用ADM3053有以下优势:

(1)功耗低体积小。采用了基于电磁隔离原理的iCouple信号隔离专利技术。功耗相当于同数据传输率下传统光电隔离器的1/10.同时采用了基于高频开关的芯片级变压技术isoPower实现供电隔离。在CAN 协议控制器与物理层总线之间创建一个完全隔离的接口。使得元器件数量减少,节约电路空间,简化了接口设计,降低了设计复杂度;

(2)性能更高。在时序精度、瞬态共模抑制力、通道间匹配性能均优于传统光电隔离器;(3)产品成本更低。每个通道成本相当于传统光电隔离器的40%.

1.2 ECAN模块结构

ECAN的接口与结构电路如图2所示。ECAN具有32位内部结构,包括协议内核(CPK)和消息控制器。

在协议内核CPK 收到一个来自总线的消息后,消息控制器中的接收控制单元确定是否把接收的消息存储到32 个消息邮箱RAM 中的某一个中。接收控制单元要检验消息的状态、标识符和消息对象的屏蔽来决定邮箱的位置。接收的消息经过滤波后存放到第一个邮箱中。如果接收控制单元不能找到任何一个存储接收消息的邮箱,则消息被丢弃。

一个消息有11位或29为标识符、一个控制域和最多8个字节的数据构成。当要发送一个消息时,消息控制器把这个消息发送到CPK 的发送缓冲区中,以便在下一个总线空闲状态时开始发送消息。当多于一个消息要被发送时,最高优先级的消息将被消息控制器发送到CPK中,如果两个消息的优先级相同,则大序号的邮箱首先发送。

1.3 接口电路设计

本文使用的接口管理CPU 为TMS320F2812,使用其内部集成的ECAN模块,因此只需要连接CAN总线收发器模块和隔离器件即可实现CAN总线接口功能。

ECAN接口电路图如图3所示。

ADM3053的左侧为逻辑端,逻辑端管脚接线如下:

(1)RXD 和TXD 分别接DSP 的ECANRX 和ECANTX引脚;

(2)VCC接逻辑端VCC(+5 V)电源;

(3)VIO接DSP的IO供电电压VIO;

(4)GND管脚接逻辑端地线端GND_LOG.

ADM3053 的右侧为总线端,总线端的管脚接线如下:

(1)CANH 和CANL 之间与CAN 物理总线相连,且确保总线两端并联120 Ω端接电阻;

(2)总线端电压输入VISOIN 接隔离电压输出VI-SOUT,并通过滤波电容接地;(3)CANH和CANL连接共模电感ACT45B-510-2P,滤除总线上的共模信号;

(4)CANH和CANL并联TVS管PESD1CAN,作为瞬态抑制保护,防止总线上的瞬变干扰。

2 软件设计

2.1 ECAN的存储器映射ECAN的寄存器被映射到片内存储器的外设帧1区域,CPU 用这些寄存对CAN 的消息对象进行配置和控制,控制和状态寄存器只允许32 位存龋ECAN 提供了32个消息邮箱,每个邮箱可以配置为发送或接收邮箱。消息是一块RAM 区域,映射到DSP 的RAM 存储器,每个邮

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)