基于DM6446 中的高清数字视频显示接口设计方案

本文通过直接对芯片内部PLL以及VENC时序发生器的配置,产生显示高清数字视频所需的像素时钟和同步控制时序信号,VENC 的输出再经由TFP410提供的DVI显示接口,最终实现了720P,1080P以及WUXGA分辨率下的高清数字视频显示,最终说明了本文所提出方案是易用、可行,具有实用性。

0 引言

TI 公司推出的DM6446 芯片在视频处理领域被广泛的使用,其基于ARM+DSP 双核架构,同时具备了通用处理器(GPP)和专用数字处理器(DSP)的功能。它的视频处理子系统(VPSS)同时包含了视频采集的接口-- 视频处理前端(VPFE),以及视频显示的接口--视频处理后端(VPBE),这也是其能够在视频处理领域崭露头角的重要组成部分。DM6446能够同时支持标准时序PAL/NSTC制式的数字和模拟视频输出,也支持非标准模拟VGA显示接口,但这模式的视频输出的分辨率都较低,不适用于需要大分辨率显示的场合。

要让其支持高清显示,就必须通过编程配置,实现高清显示所需的时序控制信号。DM6446 支持并行的24位RGB888视频数据输出,经过外部芯片编码转换后送给显示器显示。这里采用的编码芯片是TFP410,它接收并行的图像数据以及同步控制信号,经过编码转换后,按照DVI标准传输给显示器进行显示[5].

文中第1 部分介绍了高清数字视频接口设计的整体结构;第2部分介绍了TFP410的配置和使用方法;第3部分介绍了实现高清数字显示所需的VENC的参数配置方法,同时结合OSD 窗口配置给出了实际的高清数字视频显示结果。

在目标板上,720P(1 280×720@60 Hz)、1 080P(1 920×1 080@60 Hz)以及WUXGA(1 920×1 200@60 Hz)分辨率的数字视频显示都能够稳定运行,说明这里提出的高清数字视频显示接口设计方案是正确、可行的,对基于DM6446高清数字视频显示应用具有实际意义。

1 高清数字视频显示接口整体结构

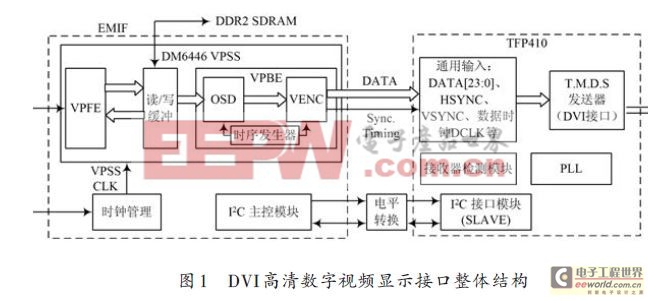

整个DVI 高清数字视频显示接口的结构如图1 所示,主要可分为DM6446 的VPSS 接口部分以及DVI 驱动器TFP410接口两部分。

VPFE从外部采集到视频数据后存储于DDR2中的指定位置,VPBE 中的在屏显示模块(OSD)也在DDR2中有对应的缓冲区,这些模块与DDR2之间的数据传输都有专门的读写逻辑控制,以保证数据的传输带宽满足系统要求。对于高清显示的支持,主要是对VPBE中的视频编码模块(VENC)的时序控制部分的正确配置,包括VENC时钟、OSD时钟和输出给TFP410的像素时钟,以及视频的行同步、场同步信号等,这些在后面会有具体介绍。

TFP410 主要起到视频数据编码的作用,将前面由VENC 输出的图像数据以及同步控制信号经编码后用差分串行的方式(T.M.D.S)传输给显示器,这可以保证数据在传输过程中的抗干扰能力。同时,TFP410 包含有一个I2C 接口,使得DSP 可以通过它配置DVI驱动器的工作模式。在系统上电后,TFP410 能够检测到显示器是否连接,这样DSP便可以通过检查相应的状态位来决定是否发送视频数据。

2 TFP410 的工作模式配置

TFP410 支持的最高像素时钟为165 MHz,能够满足高清数字视频显示的需求,其总共有两种配置方法:

引脚直接配置法和I2C配置法。采用引脚直接配置的方法,上电后芯片可以直接工作在既定模式下,但是功能比较单一,工作模式不够灵活。采用I2C配置的方法,便可以根据需要调整芯片的工作模式,包括数据采集的时钟沿、数据位宽、数据采集延时等。通过读取TFP410中的相关状态寄存器,DSP端的应用程序还能够获得图像传输的相关信息,包括水平、垂直全局分辨率,以及显示器是否连接等。

TFP410的I2C 可访问寄存器共有256个,其中绝大多数是保留使用的,在实际使用中,需要操作的寄存器更是少数。在这里,只需配置寄存器CTL_1_MODE、CTL_2_MODE、CTL_3_MODE 即可,其他的都可以按照默认配置,一般情况下无需改变。设置CTL_1_MODE.

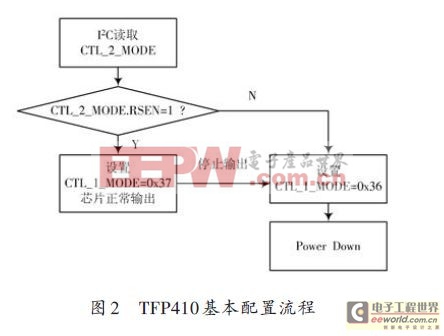

PD#=1 使芯片从节电模式恢复到普通模式;设置CTL_1_MODE.HEN=1、CCTL_1_MODE.VEN=1使能行、场同步信号输入,设置CCTL_1_MODE.TDIS=0 使能芯片T.M.D.S 电路输出。CTL_2_MODE主要用于主机检测显示器状态,而CTL_3_MODE 则主要负责数据采集过程中的时延控制。对TFP410 的基本配置流程如图2所示。

在图2 中,仅仅是列出了必须配置的寄存器,其余寄存器可以不用修改,一般不影响使用。配置CTL_1_MODE=0×37,使器件工作模式为:24 位数据宽度、单端像素时钟(VCLK)输入、在VCLK 上升沿采样输入数据。配置好TFP410后,DM6446只要按照高清数字视频的标准时序输出相应的图像数据和同步控制信息,就能够将OSD 上的内容通过DVI 接口显示到LCD 显示器上。

3 VENC及OSD配置

3.1 VENC配置

当

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- 基于TMS320DM6446的H.264编码器实现与优化 (02-18)

- 基于Davicn的嵌入式网络智能视频监控系统设计(06-04)

- 达芬奇技术在视频和机器人方面应用案例及技术文献汇总(01-29)

- 一种基于软件关机电路的电源系统设计方案(07-04)

- 嵌入式网络智能视频监控系统设计方案(02-19)