一种基于软件关机电路的电源系统设计方案

摘要:为了实现嵌入式虹膜识别系统的稳定工作,提出了一种基于软件关机电路的电源系统设计方案,并完成系统的硬件设计。该系统的硬件设计主要分为全局电源,内核电源和I/O模块电源3大部分,能够满足虹膜识别系统的所有器件功耗需求。实际应用表明,该电源具有软件可操作性,能够使内核达到长期且稳定工作的特点,满足了设计需求。

关键词:嵌入式虹膜识别系统;DM6446;软件关机电路;内核电源

随着社会和科技的发展,身份认证的重要性日益显现。传统的身份识别方式由于其固有的局限性已远远不能满足要求,于是迫切希望有一种安全可靠、易于使用的鉴别身份方式。虹膜识别以其非接触的采集方式,最精确的识别方法,居于生物特征识别系统的首位。目前,虹膜识别系统实现平台可分为基于PC机的虹膜识别系统和基于嵌入式的虹膜识别系统两大类。前者主要用于国防等国家大型管理系统等领域;而后者适用于小范围认证,信息处理量不大,系统结构较为简单的高安全级别门禁系统等领域。

本课题研究开发了基于DM6446的嵌入式虹膜系统,主要研究工作分为3部分:虹膜嵌入式硬件系统的实现、Linux操作系统下驱动编写和虹膜算法在DSP上的移植与优化。本文重点阐述在该嵌入式硬件系统实现过程中的电源设计。根据业界硬件工程师的设计电路经验,电源设计是电路设计的核心,只有电源在长期稳定地工作条件下,嵌入式系统的各个模块才可能完成其相应的工作。因此,电源的设计与实现在该嵌入式系统中占有至关重要的作用。

1 全局电源设计

在本系统中,通过考察各模块电路和芯片参数等多方面因素,确定了整个系统的全局电源为5V输出;由于DM6446中的ARM内核和DSP内核等均为高功耗模块,所以在全局电源设计中,应考虑系统的最大功耗,使其能维护整个模块系统能正常稳定工作,并杜绝过度发热现象。

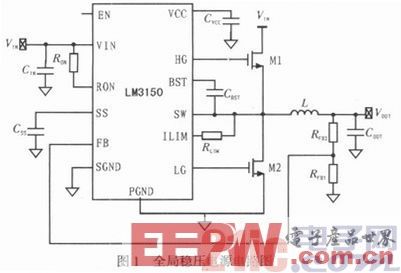

综上所述,定义全局电源输出电压:Vo=5 V,负荷电流:Io-TYP=12 A,输入电压Vin-TYP=12 V,软启动时间tss=5 ms。选用LM3150降压电源芯片,其输入电压范围可达到6~24 V,输出电流最高达12 A,达到设计要求。

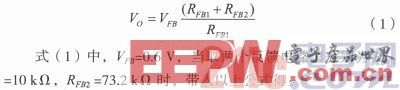

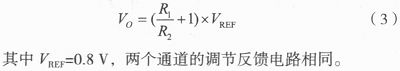

1.1 设计输出电压

全局稳压电源电路图如图1所示,根据输出电压计算公式:

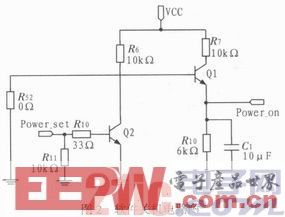

1.2 使能端软件关机电路

该电路使用隔离的小电压控制LM3150电源的使能引脚(EN),保证了单片机控制电路引脚不受倒灌的高电压侵害。

软件关机电路图如图2所示,在调试阶段,焊接R52电阻,使得Q1基极为低,Q1断开,Power_On端经R10接地,使得LM3150电源电路停用;当不焊接R52电阻时,Q1基极为高电平,Q1导通,此时,Power_on端电压

,由于VPower_on>1.26 V时,启动LM3150电源电路。(注:此时的VPower_on可依据电阻的不同阻值任意调节,实现了小电压控制某大电压通断)

在软件关机电路中,将单片机的引脚连接到Power_set端,当Power_set端为高电平时,Q2导通,使Q1基极为低;当Power_set端为低电平时,Q2断开,使Q1基极为高电平。以实现用单片机控制整个电路电源的通断,并解决了LM3150反馈电流倒灌使单片机烧毁的问题。

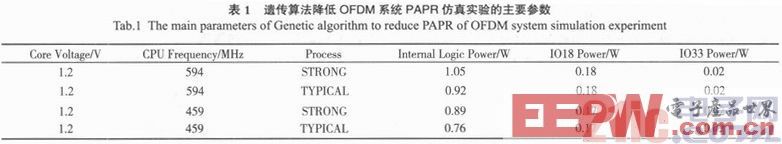

2 内核电源设计

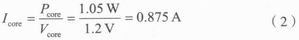

根据DM6446内核功耗表,如表1所示,在频率达到594 MHz的情况下,内核电压为1.2 V,功耗为1.05 W,内核所需电流为:

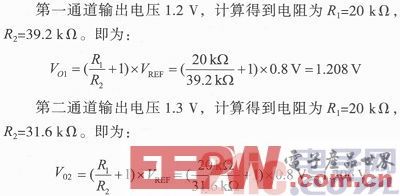

本系统设计时,采用了810 MHz的DM6446,其内核功耗会高于1.05 W,所需内核电流也高于0.875 A,其内核电压为1.3 V;并且在系统板中的FPGA(EP3C55F780)所需内核电压为1.2 V,综上两种因素的考虑,因此,其一,内核电源需提供1.2 V和1.3 V两种不同电压;其二,为使810 MHz的DSP内核能稳定工作,需为其提供功耗余量,提供的最大电流控制在3A左右。

设计时采用TPS54386电源芯片,它不仅能提供最大为3 A的大电流,而且还是双电压输出模式。内核电源的典型电路图如图3所示。

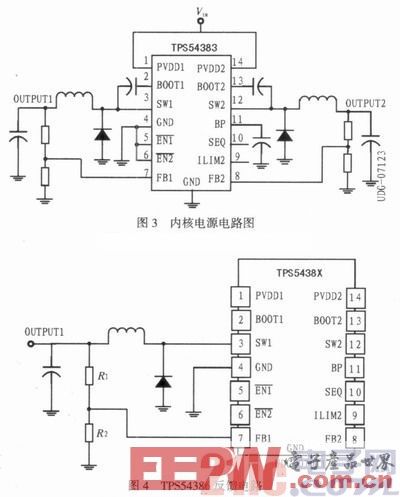

设计反馈电阻R1和R2以保证输出电压为理想输出电压。如图4所示TPS54386反馈电路。

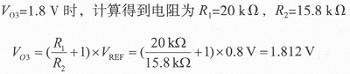

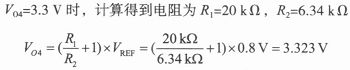

3 I/O模块电源设计

对于DSP外围I/O口模块电压分别为1.8 V和3.3 V,同样采用TPS54386电源芯片,依据以上的设计方法:

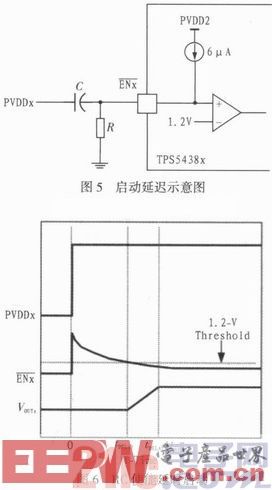

在设计过程中,如图5,图6所示,考虑到DSP内核的上电时间应比I/O模块的上电时间提前或同时发生,而两模块供电又是分开的,因此需设计硬件延迟电路。

(其中,VTH=1.2 V、IENX=6μA、R=51 kΩ),这里取C=12 pF时,延迟时间为tDELAY=100 ns。

3.1 CVDD和CVDDSP的隔离

ARM内核和DSP内核上电顺序如图7所示,DSP内核的上电时间晚于ARM内核的上电时问,ARM上电后,使整个系统开始正常运转,而进行数据处理的DSP内核应在ARM上电一段时间后上电或不上电。所以对

- 基于FPGA的混沌加密虹膜识别系统设计(06-04)

- 大热的虹膜识别系统的硬件设计与实现,系统方案、软件流程、算法设计(06-04)

- 基于TMS320DM6437的虹膜采集和识别系统设计(10-22)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- 基于TMS320DM6446的H.264编码器实现与优化 (02-18)

- 基于Davicn的嵌入式网络智能视频监控系统设计(06-04)