利用FPGA解决手持设备MPU功耗问题

开关的速度决定了功耗的大校影响动态功耗的另外一个因素是电路内部结构中形成的固有电容。动态功耗是时钟频率、正在开关的门数量和这些门开关速率的函数。门扇出和走线上的电容负载会增加动态功耗,并且功耗值正比于电容、电压和频率平方的乘积。

设计人员对这种功耗具有最大的控制能力,他们可以利用许多技术实现动态功耗的最大改善。降低信号开关频率可以使功耗呈指数式下降。正如图1所示,用于UART的控制逻辑、奇偶校验或帧超限错误都发生在速度较低的时钟域。即使门数没有减少,功耗也会下降。设计人员还可以通过降低整体工作频率(如果可行的话)来减小动态功耗。例如,在完成可行性和性能分析后,设计人员决定上述设计不仅能工作在133MHz,也能工作在66MHz。DSP支持这两种速率,而减小电压也有助于降低功耗。

另外一种技术是减少处于工作模式的有效门数。有时某部分逻辑虽然在开机时被打开和配置,但实际上不要求做任何事情。例如,模拟音频捕获单元处于工作状态,设备却不在执行任何数字SPDIF音频捕获。在这种情况下,一般的数字SPDIF音频捕获电路仍将执行数据采样、双相解码等工作,因而无谓地浪费功率。如果禁用整个数字SPDIF音频捕获电路,使电路中不发生任何信号开关动作,那么动态功耗将会显著降低。

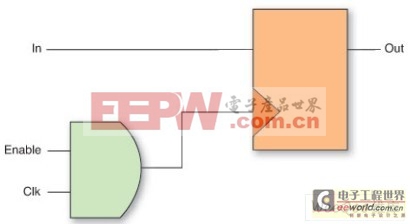

设计人员可以禁用传送到这部分电路的时钟来达到这个目的。一种简单的做法是将时钟信号与使能信号相“与(AND)”,如图2所示。如果使能信号是低电平,那么与门的输出将保持低电平。如果使能信号为高电平,与门将输出时钟信号。

图2:一种简单的时钟选通机制。

还可以使用其它方法。如果可能并且拓扑又支持的话,可以通过复接地址和数据线来减少信号线数量。在我们这个例子中,到视频编码器的输出是16位数据,我们可以把它复接成8位,然后分别在时钟的两个沿(上升沿和下降沿)发送出去。这样做也能节省动态功耗。此外,选择串行接口代替并行接口也能降低功耗。使用带较低电容负载的LVTTL或LVCMOS I/O也很有用。

嵌入式处理器

将处理器嵌入到FPGA中是手持设备设计人员可以采用的又一种策略,它可以带来很多好处。首先,减少了定制处理器带来的上述挑战。其次,外设和处理器之间的交互发生在FPGA内部,因而可以减少I/O数量。由于I/O会消耗相当多的功率,此举也能达到一定程度的节能效果。赛灵思的Virtex-5版本支持PowerPC 440处理器、硬处理器和MicroBlaze软处理器,所有这些处理器都可以被设计人员用来创建高端或低端应用系统。

随着90m和65nm半导体技术的发明,门的尺寸在不断缩小,导致静态功耗问题越来越突出,在对功耗指标越来越敏感的今天,这是一个极具挑战性的现象。由于功耗问题获得了众多FPGA供应商的重视,在这个领域中已出现许多令人兴奋的新技术。低功耗设计将决定一个系统的集成能力有多强,业界也迫切需要将注重功耗的设计技术标准化

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)