一种基于DSP的人工耳蜗语音处理器设计

1 带自适应噪声消除技术的CIS算法

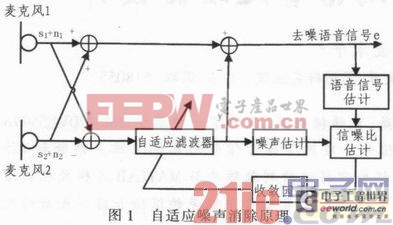

1.1 自适应噪声消除原理

在低信噪比的环境下,耳聋患者的语音识别率大幅下降。基于自适应滤波器的噪声消除法能有效的增强语音,消除背景噪声,从而提高患者的语音识别率。本文中语音采集部分利用了两个麦克风接收语音,经过采样后作为两个通道的输入信号,输入信号中均包括语音信号成分s和噪声成分n。假设麦克风1的采样结果为s1+n1,麦克风2的采样结果为s2+n2。由于麦克风1和麦克风2分别对同一环境中的声音进行采样,s1和s2为相关信号,n1和n2为相关信号。假设麦克风1和麦克风2收到的语音信号一样,即s1等于s2。通过两路信号相加得到主通道输入信号x1=2s1+n1+n2,通过两路信号相减得到参考通道输入信号x2=n1-n2。由于主通道语音中的噪声n1+n2与参考噪声n1-n2是相关的,参考通道中的自适应滤波器在接收n1-n2以后使输出在最小均方误差下最接近主通道噪声n1+n2。输出端e得到了消除噪声后的增强语音信号。本文中自适应滤波器采用了归一化LMS算法,当信噪比较大时,采用较小的收敛因子,减少稳定失调误差;当信噪比较小时,采用较大的收敛因子,加快算法的收敛速度。自适应噪声消除原理如图1所示。

1.2 带自适应噪声消除技术的CIS方案

文中设计的人工耳蜗语音处理器采用CIS方案,即连续间隔采样方案(Continuous Interleaved Sampling,CIS)。语音信号先经过预加重处理,以补偿语音信号中的高频成分,然后做FFT变换,经n个带通滤波器后划分为与刺激电极相对应的通道,对各个通道能量求和并利用对数或指数函数压缩已提高患者的听力动态范围。带自适应噪声消除技术的CIS方案如图2所示。

2 硬件结构与设计

本系统以TMS320VC5509A DSP为核心,TLV320AIC23语音Codec芯片等其他外设为辅助设备。TMS320VC5509A控制系统的外设和处理CIS算法程序,TLV320AIC23对外部声音进行采样和A/D转换。TMS320VC5509A是TI公司推出的一款高性能低功耗的16位定点数字信号处理器,它拥有丰富的片内资源,能方便的控制其他设备,输出处理结果等。TLV320AIC23具有很低的功耗,在ADC和DAC的噪音可分别达到90 dB和100 dB。此外TLV320AIC23支持MIC和LINE IN两种输入方式,内部ADC和DAC转换模块均带有完整的数字滤波器,可以在8 kHz到96 kHz的采样频率范围内传输数据宽度为16位,20位,24位,32位的数据。

语音采集芯片TLV320AIC23与主处理芯片TMS320VC5509A的接口电路如图3所示。

DSP与AIC23的接口有两个,一个是控制接口采用I^2C模块,通过编程完成对AIC23的配置;一个是数据音频接口,通过MCBSP0传输数据。

AIC23的控制接口有SPI/和I^2C两种工作方式,由于VC5509A片内外设含有I^2C模块.因此使用I^2C方式控制AIC23更为方便。此时VC5509A作为I^2C总线的主设备,AIC23作为从设备。在I^2C总线上AIC23有7位外设地址,9位寄存器的设置值。SCL和SD1分别是AIC23的控制端口和数据输入端,分别和VC5509的I^2C模块端口SCL,SDA相连。TLV3320AIC23的数据音频接口支持右判,左判,I^2S和DSP 4种接口模式。本系统采用DSP模式,把AIC23设为主模式,DSP设为从模式,即MCBSP0的移位时钟和帧同步时钟全部由AIC23提供。在帧同步脉冲到来时第一个数据字即为左通道数据,右通道数据紧跟着左通道数据。

语音是时变的,非平稳的随机过程,但由于语音的形成过程与与人类发音系统的生理结构密切相关,通常假设语音信号是短时平稳的,即在10至30 ms的时间段内其频谱特性和一些物理特征参量可近似的看作是不变的。因此语音信号要进行分帧处理,在采样率为8 kHz时可将帧长取为N=256较为合适。

3 系统软件设计

本系统中语音信号由LINE IN输入,LLINE IN和RLINEIN分别对应自适应噪声消除原理图中的麦克风1和麦克风2,语音信号分别经过AIC 23内部的A/D转换后,通过MCBSP0通道传送到VC5509A内。VC5509A对这些语音数据进行CIS算法处理,得到各个通道的刺激脉冲。

系统软件设计分为系统初始化,系统中断处理程序和CIS算法程序。系统的初始化包括设置时钟发生器,MCBSP初始化,I^2C初始化以对AIC23控制寄存器的配置。系统中断处理程序设置一个标志位,每中断一次左右声道各采集一个数据,当采集满一帧时能使采样值保存在两个数据缓冲区的另一个缓冲区中。系统中主程序一直处于循环处理过程,在一帧信号执行完CIS算法程序后,等待下一帧信号接收完毕,然后重新执行CIS算法程序。为保证语音信号处理的连续性,CIS算法处理时间应当小于一帧数据的采样时间。本系统CPU时钟为144 MHz,采样频率8 kHz,中断频率8 kHz,因此每125μs采集一个点,采集一帧256个数据需32 ms,即每隔32 ms输出1个刺激脉冲,CIS子程序运行一次需23.1 ms。图4为系统设计流程图。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)