强化DPD演算效能SoC FPGA提升蜂巢网络设备整合度

蜂巢式网络服务供应商对降低营运成本的需求愈来愈迫切,因此现场可编程门阵列(FPGA)业者推出整合嵌入式处理器的SoC FPGA方案,并导入效能更高的数字预失真(DPD)演算法,协助网络设备制造商以更低功耗及成本,打造更高生产力的产品。

蜂巢式网络业者设法透过全新传输界面、传输频率、更高频宽以及增加天线的数量和更多无线基地台提升网络密度,因此须要大幅降低设备的成本。另外,这些业者为降低营运成本,也需要更高运作效率和网络整合度的设备。无线基础设备制造商为提供可以符合不同要求的设备,皆在寻求更高整合度、更佳效能和灵活度高的解决方案,并且同时降低功耗和成本。

整合度是降低整体设备成本的关键,然而这必须依赖可提升功率放大器效率的高阶数字演算法来降低各项运作成本,其中一项最常用的演算法是数字预失真 (DPD)。由于设备的配置愈来愈复杂,因此提升设备运作效率是一项很大的挑战。藉由先进长程演进计划(LTE-Advanced)传输技术,无线传输频宽可达到100MHz,如果厂商试图用连续频谱配置结合多种传输界面,频宽甚至可以更高。主动天线阵列(AAA)和支援多重输入/输出(MIMO)技术的远端无线单元(RRU)所需的演算法对频宽的要求愈来愈高。本文将探讨业界完全可编程系统单芯片(All Programmable SoC)元件如何为目前和未来的数字预失真系统提升效能增益,同时也可为设备厂商提供充裕的可编程能力、低成本和低功耗,并加快产品上市时程。

建置蜂巢式无线网络

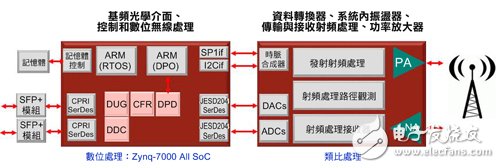

业界完全可编程SoC元件结合高效能可编程逻辑(PL)架构,其中包含序列式收发器(SERDES)和整合硬件处理子系统(PS)的数字讯号处理器 (DSP)模块。这个硬件处理子系统内含一个双核心安谋国际(ARM)Cortex-A9处理器、浮点运算单元(FPU)和NEON多媒体加速器及一系列丰富的周边功能,包括通用异步收发器(UART)、串列周边界面(SPI)、内部整合电路(I2C)、以太网络(Ethernet)和记忆体控制器等完整无线传输所需的周边功能。有别于外部通用处理器或DSP,可编程逻辑和硬件处理子系统间的界面有大量连结,因此其频宽可以非常高;但如要用独立式解决方案处理这些连结,却不可行。此外,完全可编程SoC元件还包含硬件和软件阵列,因此可在单一芯片内建置远端无线单元所需的功能,如图1所示。

图1 在这个典型的无线架构中,所有数字功能可整合在单一元件中。

可编程逻辑中丰富的DSP资源可用于建置数字上行转换(DUC)、数字下行转换(DDC)、峰波因数抑制(CFR)与数字预失真(DPD)等数字讯号处理功能。此外,SERDES可支援9.8bit/s的通用型公共射频界面(CPRI)和12.5bit/s JESD204B,分别用于连接基频和资料转换器。

硬件处理子系统同时支援对称式多重处理技术(SMP)和非对称式多重处理技术 (AMP)。在这个案例中预定会采用非对称式多重处理模式,因为其中一颗ARM Cortex-A9处理器被用于建置基板层级的控制功能,例如讯息终止、排程、设定等级以及警示执行(裸机或更有可能是如Linux等作业系统)。而另一颗ARM Cortex-A9处理器则用以建置部分数字预失真演算法,因为数字预失真演算法并不保证整体都是硬件的解决方案。

数字预失真可藉由扩大其线性范围提升功率放大器效率;当驱动放大器进一步增加输出功率时,即可提升运作效率,而静态功耗会相对维持正常。数字预失真为扩充其线性范围,会使用放大器中的类比反馈路径和大量数字处理功能计算放大器的逆向非线性系数。然后利用这些系数预先校正与驱动功率放大器的传输讯号,最终可增加放大器的线性范围。

数字预失真是一个封闭回路系统,其会撷取先前的传输讯号来决定放大器与这些传输讯号的传输方法。数字预失真的第一个任务是要让放大器与先前的传输讯号达成一致,这个过程会在一个校准模块中进行。在执行任何演算法运算前,系统会用记忆体来校准资料;资料一旦妥善校准后即可运用自动相关矩阵运算(AMC)和系数运算(CC)演算法,建立代表功率放大器逆向非线性系数的最近值。一旦产出系数后,资料路径前置失真器即运用资料预校准被传输到功率放大器的讯号。

加速估计数字预失真系数

当然,这些功能可以透过许多不同的方法建立。有些比较适合用软件的方法,而有些则适用硬件,同时也有是软硬件皆适用;然而,最终还是要以所需的效能决定建置的方法。采用完全可编程SoC元件可让系统设计人员自由支配硬件和软件的最适度使用情况。就数字预失真的情况而言,由于需要非常高的采样率,因此内含高速过滤功能的资料路径预失真器通常会建置在可编程逻辑中,而产生数字预失真系数的校准和估算引擎则可

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)