一种基于FPGA的高速超声波采集模块设计

时间:03-10

来源:互联网

点击:

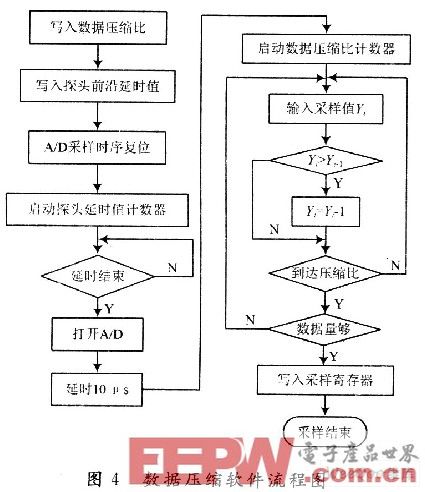

直至压缩比计数到零后,得到一个有效的采样数据。同时压缩比计数器自动复位,重新开始计数,其工作流程如图4所示。

2.3.3 数据缓冲

为了解决前端数据采集与后端数据传输在速率上的不匹配问题,在FPGA内部设置一块数据缓冲FIFO,大小为8K×16 b,压缩后的数据直接存储到FIFO中,而微处理器对FIFO中数据的读取通过中断方式完成。数据缓冲FIFO通过core generator例化,只需要少量的读/写控制逻辑就可以使FIFO正常工作,而且FIFO的大小可以在FPGA提供的RAM位数范围内灵活设置。下面给出例化后的FIFO的VHDL语言描述:

保存在FIFO中的数据通过这些逻辑控制端口便于微处理器对其进行读取、清零等操作。

3 结语

设计的基于AD9446的数据采集模块采用FPGA实现数据采集控制、数据压缩及数据缓冲等功能,简化了硬件电路,提高了模块的可靠性和稳定性,并有利于模块的功能升级。同时采用高速高精度模/数转换器满足了数字式超声波探伤系统对数据采集精度方面的要求。另外,FP-GA对数据进行的预处理,方便了微处理器对数据的调用和后处理。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)