电控喷油雾化检测的DSP和FPGA通信模块设计

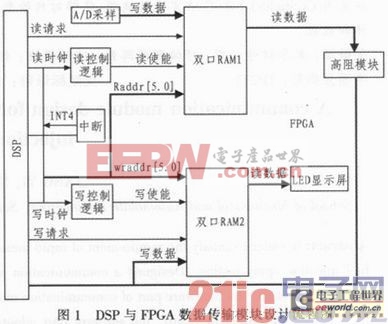

基于DSP的FPGA通信模块设计流程如图1所示。首先在FPGA中创建双口RAMl和RAM2,A/D采样的数据传送到RAMl中,然后RAM1中的数据经过EMIF被读入到DSP中进行实时处理运算,处理后的结果数据在经过EMIF写入到RAM2中,RAM2可以外接LED显示屏显示处理运算结果。在此过程中,RAM1和RAM2共用地址总线和数据总线,在RAM1读和RAM2写数据总线之间插入高阻模块,以防止数据总线冲突。3 通信模块软件实现

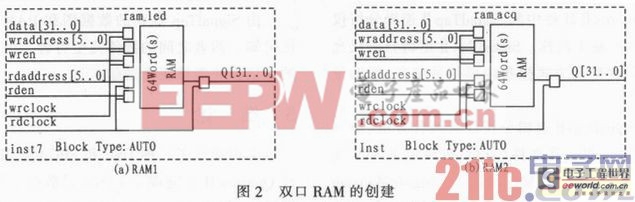

RAM1和RAM2都是有一个读端口和一个写端口,存储大小为6432位,数据总线和地址总线都是32位,独立的写时钟和读钟。不同的是RAM1中导入了初始存储内容(./0517.hex)。

0517.hex中的部分内容如下:

:04000000C000002AD2

:040001000000004487

:040002000000006496

:040003000000008871

:04000400000C008048

:04000500000000D91E

:040006000000102F3

在QuartusII中用原理图的形式创建FPGA与DSP数据传输模块,如图3所示。

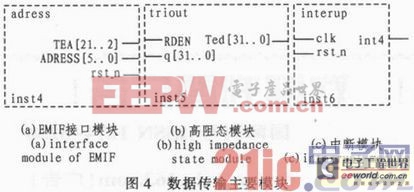

主要的功能模块:1)EMIF接口模块,如图4(a)所示,该功能模块为DSP与FPGA中的双口RAM进行数据传输提供地址和数据总线。2)高阻态功能模块如图4(b)所示,该模块的主要功能是防止总线冲突。3)中断功能模块如图4(c)所示,该功能模块为时钟中断,负责双口RAM读和写的时间控制。

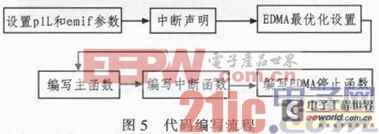

本论文中应用CCStudi03.1集成开发环境并结合C语言编写DSP与FPGA的数据传输的代码。编写流程如图5所示。

4 数据传输验证

4 数据传输验证

在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizard Plug-InManager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。图6给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

用QuartusII提供的Signal Tap仿真获取数据,如图7所示。

由SignalTap截获的数据图和RAM1中存储的初始值对比可知,两者之间的数值完全符合,由此可知DSP与FPGA的通信模块能够正常通信。

5 结论

文中设计了一种DSP和FFGA数据传输的通信模块,通过Quartus II上完成了FPGA对数据采集系统的时序控制的设计,利用C语言编写DSP与FPGA之间的通信控制代码,应用Quartus II中的Signal Tap功能验证了DSP与FPGA之间数据传输的正确性,证明该通信模块能够实验电控喷油雾化检测快速测量和处理大量的数据的要求。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)