一款基于FPGA的I2C总线的设计方案

0 引言

由于在嵌入式系统开发中越来越多的应用到FPGA,而一些嵌入式CPU,比如STM32 为了降低成本,减小封装尺寸,没有外接专门的CPU 读写总线,而只提供了一些如SPI 和I2C 的接口。而且在应用中经常有数据要配置到FPGA 中,如FPGA 中的应用配置寄存器,和配置表项等,都需要CPU 配置。这些数据的数据量不大,速度也不要求很高,很适合用I2C 总线来配置。

I2C 总线是Philips 公司设计的一种控制和配置内部IC 双向两线的串行总线。主要特点是接口信号线较少,但是其数据的传送速率不是很高,其高速模式下为3.4Mb/s.应用于配置FPGA 比较适合。在通常的应用中嵌入式CPU 作为MASTER 模式的主器件,FPGA 作为SLAVE 模式的从器件。通过使用I2C 总线,减少了CPU 和FPGA 的连线,而且嵌入式CPU 一般有内含I2C总线控制器,使得CPU 和FPGA 间的通讯硬件电路简化。

1 I2C SLAVE 模式整体结构的分析设计

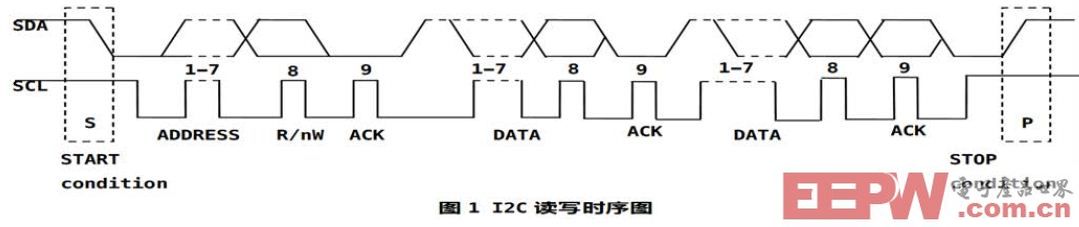

I2C 总线要求两条信号线,一条串行数据线 SDA,一条串行时钟线 SCL.通过串行方式传送数据。它是一个多主器件的总线,如果两个或更多主器件同时传输数据,可以冲突检测和仲裁。为简化设计和满足应用要求,该设计实现一个标准I2C总线的子集。完成1 字节的单次读写和连续读写功能。所以这就要求应用中的I2C 总线上只能有一个主器件,而FPGA 逻辑则只能当成从器件。I2C 总线的两条信号线都是开漏的,必须外接上拉电阻,以保证总线空闲时,总线都处于高电平。I2C的读写时序图如图1.

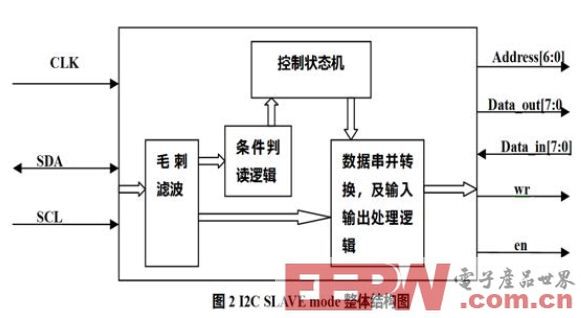

从图1 中可以看出,总线的起始条件为在SCL 为高电平时,SDA 拉低产生一个下降沿。而总线的停止条件为在SCL 为高电平时,SDA 释放由上拉电阻产生一个上升沿。在快速模式下,SCL 时钟频率最大值为400KHz,SCL 时钟的低电平周期最小为1.3μs,SCL 时钟的高电平周期最小为0.6μs.在输入端,输入滤波器必须抑制的毛刺脉宽最大值为50ns.由于SCL是由主器件CPU 的内置I2C 模块产生的,所以SCL 的时序肯定符合要求。而FPGA 要采样SCL 和SDA 信号,那么FPGA 的采样时钟频率至少要为SCL 频率的2 倍以上。再加上抑制的毛刺脉宽最大值为50ns.当FPGA 的系统时钟为100MHz 时,端口以100MHz 的频率采样信号,远远大于快速模式下SCl 的400KHz,抑制的毛刺也将在5 个时钟周期内处理。而且FPGA内部逻辑一般都工作在100MHz 以上,所以I2C 模块的系统时钟可以直接使用FPGA 的系统时钟,可以省去时钟转化模块,简化处理。当I2C 总线读FPGA 时,总线主器件在发送完第一个字节,FPGA 回复ACK 后,紧接着就要FPGA 输出相应的数据,所以在FPGA 逻辑发出ACK 的同时就要开始,FPGA 的内部寻址和读取相应的数据,在SCL 时钟频率最大值为400KHz 时,FPGA 的系统时钟为100MHz,那么FPGA 的内部逻辑有约250个时钟周期的寻址时间,这个时间是完全够用的。I2C SLAVEmode 整体结构图如图2.

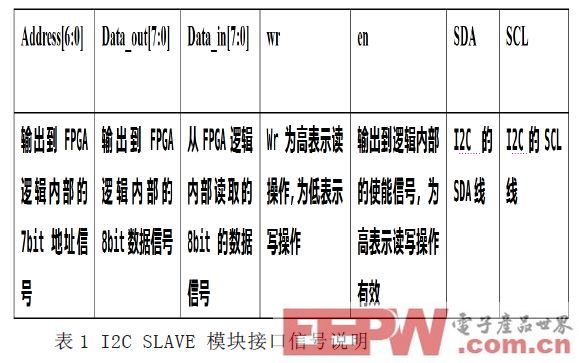

接口信号的说明如表1.

2 I2C SLAVE 模式控制器的设计与实现

2.1 I2C SLAVE 控制器的接口实现

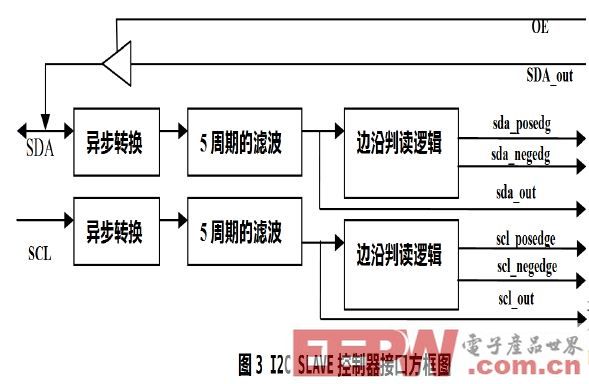

I2C SLAVE 控制器的接口部分主要包括,信号异步时钟域的转换。输入滤波器,用来抑制毛刺。及SDA 线的双向转换。由于SDA 的PIN 是双向的,所以一定要分配在FPGA 的IO BLOCK块中,只有IO BLOCK 中有双向的硬件结构。因为SDA 和SCL信号的相位相对于FPGA 逻辑的系统时钟的相位关系是不确定的。所以一定要进行异步时钟域的转换,以防止输入的寄存器出现亚稳态,它会使逻辑处在某个不确定的状态。此外FPGA的系统时钟频率比较高,对输入的毛刺比较敏感,故输入端要加入滤波器。接口部分的框图如图3.

异步时钟域的转换,采用两级寄存器的结构。输入滤波器采用5 级寄存器的结构。当采样到连续5 个高电平时,输出才为高电平,否则为低电平。接口部分的寄存器全都用FPGA 的系统时钟驱动。

2.2 I2C SLAVE 控制逻辑的实现

I2C SLAVE 控制逻辑状态机是整个模块的核心,所有I2C 总线相应的控制都由其完成。状态机有四个状态:IDLE,START,SAMPLE 和STOP 组成。Verilog 的定义如下:

`define IDLE 2'b00

`define START 2'b01

`define STOP 2'b10

`define SAMPLE 2'b11

下面介绍各个状态的功能。当I2C 总线无任何操作时控制器在IDLE 状态下,并保持。当接口逻辑判断到START 条件时,控制器跳转到START 状态下,并做好接受第一个字节的准备,包括初始化bit计数器。接着开始接受第一个字节包含7bit的地址和1bit 的读写状态位。当采集完第一个字节后,控制器跳到SAMPLE 状态下,开始执行数据字节的接受或发送。是接受或发送的状态由前一字节的最后1bit 的读写

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)