基于FPGA的湿度测量系统设计

摘要:为了实时检测常温下的湿度,以便负责人根据需要调整环境状态。采用测频计数法结合频差法设计了以FPGA芯片(EP2C8Q208C8N)为基础的可用于湿度测量的石英晶体谐振频率漂移检测电路。重点介绍在FPGA平台上通过测量石英晶体的谐振频率来间接测量湿度的方法,讨论了FPGA平台上的每个模块的设计过程,给出了部分模块和整体电路的仿真图,解释了仿真结果。FPGA参与外围硬件电路的辅助设计,会使设计更加简单,周期更短。

湿度若能够实时进行测量,对于生产、生活方面是很至关重要的,尤其是在那些仓储、种植、养殖、家庭、医疗、科研等关注湿度变化的地方。如果异常湿度不能及时被测量到,就会使生产降低、身体感到不适。现代湿度测量从机械式发展为精确度更高的电子式湿度传感器。石英压电谐振式湿度传感器就是利用了谐振元件的固有频率与被测量之间存在关系而进行测量的一种电子装置。通过在线可编程芯片FPGA来对传感器数据进行采集、测量和处理,能极大地整合和简化系统设计。文中将主要描述石英晶体(QCM)湿度测量系统中FPGA部分的程序设计,分别给出单个模块的设计思路和(或)工作流程图,对部分模块给出仿真结果,最后对总体程序进行了仿真,给出整体结果。

1 基本原理

在压电石英晶体的晶片表面涂覆湿度敏感材料,制成一个附着有吸湿膜的石英晶体谐振器。若该石英晶体放置于湿度环境中,由于吸湿膜通过氢键或者分子间作用力吸附了环境中的水汽分子,使得石英晶体的质量发生变化。根据Sauerbrey公式,如式(1)所示,为晶片上吸附水汽分子后石英晶体质量变化量,Fo为基频,△f为相同基频下的无湿敏膜标准石英晶体谐振(以下简称标准晶振)频率Fo与有湿敏膜传感石英晶体谐振(以下简称传感晶振)频率的频率差,S为晶片上湿敏膜的面积。石英晶体的质量若发生变化,其谐振频率也会随之发生变化。只要通过测量出石英谐振频率的变化量,再利用频率差-质量差-相对湿度三者之间存在的关系,由频率转换得到相对湿度。

?

?

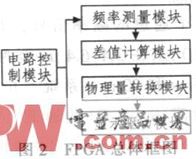

系统由湿度传感器、QCM振荡电路、FPGA平台、显示电路等模块组成,如图1所示。FPGA平台将集成测量、控制、驱动等功能模块,先通过参比对照测出两个通道的频率值,再计算两通道频率值的差,根据转换表转换出相对湿度值,送出显示。采用基频10 MHz,AT切型的石英晶体作为湿度传感器。

?

?

2 总体方案构造

2.1 FPGA芯片

FPGA,通过软件辅助编程的方式实现电路功能的一种半定制ASIC芯片。FPGA是在线可编程器件中的一种,基于查找表LUT的电路原理。N输入的查找表,将输入的真值表存储在SRAM中,系统通过“查表”的方式,输出预存结果。FPGA在电路设计和使用的过程中高度体现了以专用性、高效性,以人为本的设计思想。FPGA芯片采用的是美国Altera公司设计生产的Cyclone II系列中的EP2C8Q208C8N。它含有516个可编程逻辑块CLBs,8256个逻辑单元LEs,165888个存储位,138个可使用的I/O端口,端口最大电压为3.3 V,核心电压为1.2 V,工作适宜温度为0~85℃。

2.2 FPGA总体电路构建

FPGA程序设计是整个相对湿度测量系统设计中关键的一部分,集成了控制、测量与锁存、差值计算、物理量转换,显示驱动等模块。通过软件编程辅助设计的电路,既可降低硬件电路设计的成本,同时也发挥软件设计带来的优点。另外用FPGA做设计还可随时就应用过程中出现的问题调整程序,使系统作更大优化。整个FPGA运行的流程图如图2所示。整个FPGA电路模块的设计和仿真都将在Quartus II 9.0软件环境下完成。在FPGA中相对湿度的测量将采用实时测量的方案。

?

?

3 模块设计与仿真

3.1 控制模块

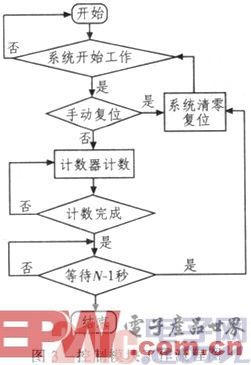

控制模块主要完成对FPGA工作进程的控制。它包括系统启动/暂停、使能控制、系统复位等功能,其工作流程如图3所示。其中N值大小可以因需求不同作数值调整。

?

?

3.2 测量与锁存模块

测量模块是FPGA设计中最关键的模块之一。为得到频率差,采用双通道分别进行标准晶振和传感晶振的频率测量。数据信号在一个闸门内的计数值很大,所以不考虑因闸门信号与数据信号不同步造成的±1字的误差。测量模块中的频率测量采用直接计数法完成。在使能高电平期间,频率信号触发沿每到来一次时,计数器加1计数;在使能低电平期间计数器数据锁存,保存至下一次的测量完成。最小测量精度为1 Hz,采用8421BCD码计数(便于观察和后续电路设计)。

?

?

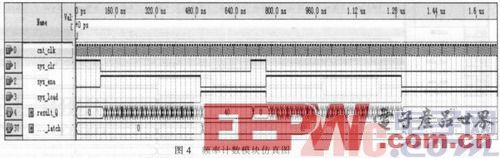

对测量和锁存模块进行仿真分析,如图4所示。从图中可以看出系统在异步复位信号sys_clr高电平下复位,否则在使能信号sys_ena高电平有效时,系统计数,直到使能无效,result

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)