基于FPGA的跳频系统设计

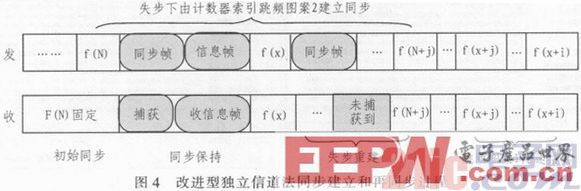

亦可在该信道下快速建立同步。改进型的同步算法如图4所示。

图4中系统开机时系统在信道f(N)建立初始同步,系统失步之后,收发双方由counter_suc指向跳频图案2的信道f(N+j),在该信道下再次重建同步。该系统中图案2用于初始同步的建立,周期短搜索时间短;图案1用于通信中传递信息,周期长搜索周期长。

3 快速同步算法的FPGA设计

上述快速同步算法在FPGA平台,采用Altera公司的Quartus2作为工具,用VHDL硬件描述语言进行逻辑功能设计。

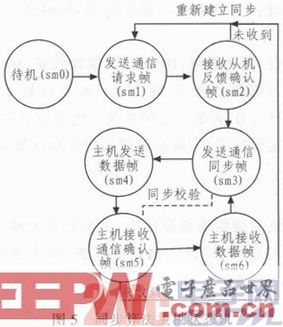

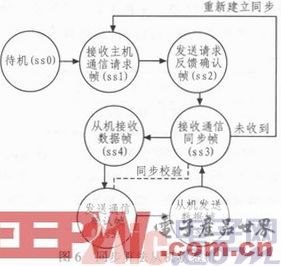

同步算法的状态机是同步实现的核心。跳频电台的主机和从机状态机如图5和图6所示。

图中所示,系统上电时主机和从机处于初始状态sm0,ss0,依照状态机流程依次执行状态转移。系统的第一次握手由主机的sm1状态发送通信请求帧实现,第二次握手则由从机的ss2状态反馈主机通信请求确认帧实现,两次握手在改进型独立信道法下快速实现系统初始同步。初始同步之后,主机sm3状态发送通信同步帧实现系统第三次握手,从机ss5状态发送通信确认帧实现系统第四次握手,两次握手保持通信中的同步状态,执行图中虚线所示的同步校验功能。

数据通信过程由主机sm4,sm6,从机ss4,ss6状态同步进行数据帧的收发。系统在同步保持状态下由图中所示环形执行状态转移循环进行数据通信,一旦系统中接收协议帧状态没接收到协议帧则系统失去同步,系统回到初始状态重新建立同步。

4 同步性能

同步时间是指建立初始同步的时间,在该算法中主要由系统跳速Rb,跳频间隔周期N和第一次第二次握手协议帧交换周期M决定。同步时钟为Tsyn,则同步建立时间Ts=M×Tsyn=(M/N)xRh。本系统跳速为900跳/s时,间隔N=386个周期,协议帧周期M=665,Ts≤0.01 s,一般系统要求同步时间Ts≤0.6s,故该算法可快速建立同步。

5 跳频系统的FPGA实现

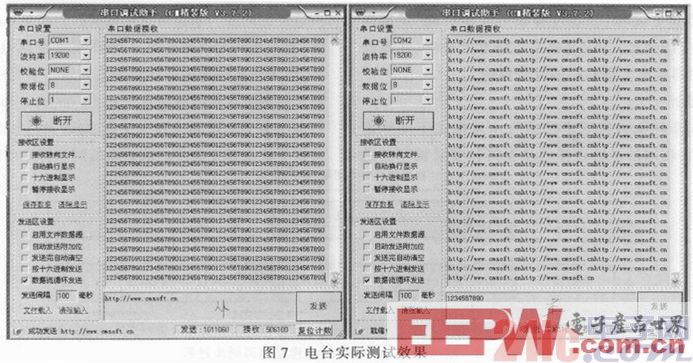

采用Altera公司的EP3C系列开发芯片作为快速同步算法的FPGA硬件实现平台,将软件设计实现的跳频系统下载到开发芯片中进行性能测试。如图7是基于该同步算法的跳频系统测试中,两个电台主机和从机之间通过上位机的串口调试工具传输数据的统计结果,其中com1是从机通过串口连接的上位机软件,com2是主机对应的上位机软件。

测试统计:主机电台:发送数据:506110,接收数据:1011060。

从机电台:发送数据:1011060,接收数据:506110。

由串口界面统计所示,两个电台收发数据无误,传输稳定。即误码率为0,表明该跳频系统工作稳定性能良好,该同步算法可稳定保持同步,满足跳频系统同步性能要求。

6 结论

文中在跳频通信系统设计中,主要对其关键技术同步算法展开研究与设计,设计了独立信道法,同步字头法和精准时钟相结合的快速同步算法。并针对独立信道法的抗截获能力弱,设计了基于双图案跳频的改进型独立信道法,即短周期图案用于同步建立,长周期图案用于跳频通信的实现过程,并分析了同步算法过程中的实现步骤,算法协议,设计过程等。由性能分析可知本文设计的同步算法可快速地建立同步,由FPGA硬件平台的实际测试可知该算法可快速地建立通信,且通信过程稳定,误码率低,具有工程实践意义。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)