基于FPGA的射频卡实时消费记录系统设计

摘要:基于使用户刷卡消费的数据可进行采集存储的目的,采用了在FPGA平台上设计一种射频卡实时消费记录系统的方法。该系统采用了FATFS文件系统,可将用户数据及时保存到SD卡之中。通过对软硬件模块和上位机的设计,采用FPGA为开发平台,对用户刷卡消费的记录写入到SD卡中。利用SD卡的移动性,可方便地实现与计算机的数据交换,达到数据分析的目的。此法便于客户对消费记录的核对,具有实际商业价值。

关键词:FPGA;NIOS II;FM1702SL;SD;文件系统

文中主要讨论射频卡实时消费记录系统的硬件和软件设计。硬件设计主要包括FPGA模块、蜂鸣器、FM1702SL模块、SD卡模块、液晶显示等模块。软件设计部分主要介绍射频读写模块的软件设计、SD卡的软件设计、FATFS文件系统移植、液晶显示和上位机对IC卡充值和加密操作。

1 硬件模块设计

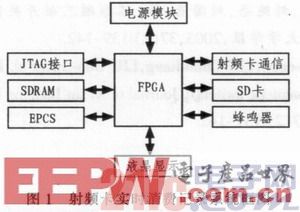

射频卡实时消费记录系统组成如图1所示,主要分为以下几部分:FPGA、电源管理、射频卡通信、SD卡、液晶显示、蜂鸣器等。

1)FPGA的选用——EP2C8Q208C8N

EP2C8Q208C8N是ALTERA公司推出的Cyclone II芯片,该芯片有8 256个逻辑单元,208个引脚、用户可用的I/O引脚为138个、18个嵌入式乘法器和2个锁相环。与其他90-nm FPGAs同类产品相比在性能上提高了60%并且减少了一半的能量消耗。基于FPGA平台设计的射频消费记录系统具有设计灵活、可裁剪、可扩充、可升级及软、硬件在系统可编程的优势。

2)电源部分

本系统通过一个开关电源提供5 V的电源。系统中FPGA的工作电压为3.3 V与1.2 V,配置芯片EPCS4S18工作电压为3.3 V,射频卡读写模块、液晶显示模块还有蜂鸣器需要5 V供电,SD卡工作在3.3 V,通过AMS1117-1.2与AMS1117-3.3稳压器把5 V的转换成1.2V和3.3V。

3)液晶显示

液晶选用带字库的LCD12864。液晶显示器工作电压为5 V,通过开关电源来供电。液晶显示系统可以显示界面,如“一卡通研发”、“卡号”、“消费”、“余额”等信息。

4)射频卡通信

考虑到开发性和经济性等因素,这里选用了复旦微电子股份有限公司设计的FM1702SL(该芯片与RC632结构类似),是基于ISO/EC14443标准的非接触卡读卡机专用芯片,工作频率为13.56 MHz,并且支持多种加密算法。射频卡我们选用的是Phihps公司的MIFARE标准IC卡,该类型卡的作用距离最大为10 cm,属于紧耦合卡。

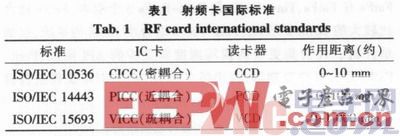

ISO/IEC组织根据接口设备与卡作用距离的不同定义了3个国际标准,如表1所示。

ISO/IEC14443标准又分为ISO/IEC14443A(代表产品是Philips公司的MIFARE射频卡)和ISO/IEC14443B(ST、MoToRoLA、SAMSung、OTI和NEC公司生产的产品)标准。

5)SD卡模块

SD卡是一种基于半导体快闪记忆器的新一代记忆设备,由日本松下、东芝及美国SanDisk公司共同研发,它具有微型、低功耗、防震、非易失性和保存数据无需能量消耗等特点,并且兼容MMC闪存卡,广泛应用于手机、数码相机、智能机器人、GPS、电子测试设备和大容量存储设备。

SD卡支持SPI和SD两种通信接口模式,由于ALTERA公司提供了SPI接口IP核,因此在我们设计的系统中采用的是SPI模式。相对SD模式,SPI模式应用的更广泛一些。

2 软件设计

2.1 射频通信模块的软件设计

系统采用的是FM1702SL非接触卡读卡机专用芯片和Philips公司的MIFARE标准IC卡共同组成了射频卡读写模块。了解S50非接触式IC卡和FM1702SL的内部结构与读写操作过程是编写程序的关键,因此对其做简单介绍。

MF1 IC S50由1KB的EEPROM、RF接口和数字式控制单元组成,能量和数据都通过天线传送,天线由几匝线圈组成并直接连接到MF1 IC S50。其与PCD之间的工作原理为:读写器向M1卡发一组固定频率的电磁波,卡片内有一个LC串联谐振电路,其频率与读写器发射的频率相同,在电磁波的激励下,LC谐振电路产生共振,从而使电容内有了电荷,在这个电容的另一端,接有一个单向导通的电子泵,将电容内的电荷送到另一个电容内储存,当所积累的电荷达到2 V时,此电容可做为电源为其它电路提供工作电压,将卡内数据发射出去或接取读写器的数据。

卡的内部有16个扇区,每个扇区分为4块,分别是块0、块1、块2、块3。块0~块2为数据块,用于存储数据。块3为控制块,包括了密码A、存取控制、密码B。每个块为16个字节,以块为存储单元。第0扇区的块0,用于存放厂商代码,已经固化不可更改。

每个扇区的密码和存储控制都是独立的,根据实际需要设定各自的密码及存储控制。在控制块中密码A和密码B各占6个字节,存储控制占4个字节,在存储控制中每个块都有相应的3个

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)