基于DSP的弹载嵌入式系统设计

摘要:基于实现目标探测识别以及高精度目标信息测量等复杂处理算法的目的,采用单片多核DSP TMS320C6678构成弹载高速多任务实时嵌入式处理平台,通过数据流处理模式的并行软件设计方法,将系统处理任务均衡分配到各处理器内核,以实现实时并行处理,提升弹栽信息处理系统的功能和性能。开展基于多核处理器的并行软件研制、充分发挥多核处理能力将成为弹栽嵌入式系统软件设计的新课题。

关键词:多核处理器;并行处理;弹载嵌入式系统;数据流模式;并行软件设计

弹载信息处理系统是一种实时嵌入式数字处理系统,用于对弹载导引系统接收信号进行分析处理,实现对目标信号的检测、截获和跟踪以及目标信息的提取,是弹载雷达导引系统的关键组成部分。随着军事技术的发展,未来空战面临着越来越严酷的战场环境,对于弹载雷达导引系统的探测能力以及反隐身、抗干扰等性能提出了更高的要求。为此需要采用复杂处理算法,如数字波束形成、空时自适应处理技术、杂波抑制、低信噪比信号检测和识别、超分辨等,提高系统目标探测和抗干扰能力。数据处理复杂度越来越大、实时性要求越来越高,同时弹载应用环境对系统功耗、尺寸又有着严格的限制,因此需要运算速度更快、容量更大、功耗更低的数字处理平台来实现这些功能需求。基于单核DSP的信号处理实现方式难以适应大运算量实时处理的新需求,传统的DSP互联技术是将多个单核DSP用高速接口连接在一起,但是这样的系统架构会带来功耗和尺寸方面的问题。采用基于单片异构多核处理器的信号处理平台成为发展趋势,以实现高速实时并行处理平台的小型化、低功耗设计,显著提高弹载信息处理系统的信号与信息处理能力。

1 多核处理器TMS320C6678性能

单核DSP其性能通常由时钟频率来评价,然而DSP的时钟频率并不能做到直线上升,单片单核结构受限于速度极限,很难再有更大发展空间;随着应用系统复杂性持续增加,只通过提高时钟频率来增强处理性能达到了极限。单片多核的结构将成为DSP发展的主流,应用单片多核处理器,将显著提升弹载雷达信息处理系统性能,并能实现弹载雷达信息处理平台更进一步的小型化。

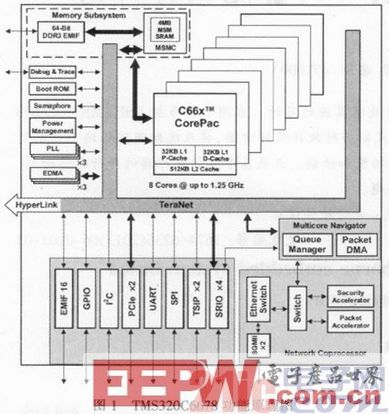

多核DSP是近年来针对高性能嵌入式应用而出现的一类多核微处理器(MultiCore MicroProcessor)。相比传统的单核处理器,多核处理器在提高并行处理能力的同时配置了更高的存储带宽和更灵活的存储结构。TMS320C6678是TI公司的最新型的KeyStone架构多核DSP,该DSP集成了8个DSP内核,每个内核频率可达1.25 GHz;定点运算能力为320 GMAC,浮点运算能力可达160 GFLOPS,运算能力比现在主流的DSP(如TS1 01)有大幅提高(TS101的内核时钟是300MHz,浮点运算能力为1 800 MFLOPS),充分体现并行处理的理念。每个DSP内核配置32 kb的一级局部程序缓存器、32 kb的一级局部数据缓存器和512 kb的二级局部缓存器。TMS320C6678的功能原理图如图1所示。

基于KeyStone体系架构,能够确保多核DSP的每一个内核发挥全面的处理功能,TMS320C6678除了具有多DSP内核导致的运算处理能力提高,还提供了丰富的对外通信接口以及存储单元的支持,增强了处理器对外高速数据交换的吞吐能力。Keystone多核架构为RISC和DSP内核以及专用协处理器和I/O的集成提供了一种高性能的系统结构,Keystone架构能够在处理器内核、外部设备、协处理器和I/O之间建立无阻塞数据传输,这主要基于多核导航器(Multicore Navigator)、TeraNet、多核共享存储区控制器(Multicore Shared Memory Controller,)和超链接总线(HyperLink)。超链接总线和高速输入输出接口实现DSP与外界信息传输,TeraNet总线结构(速度为2Tbps)把所有组成部分有机联系在一起,包括作为主要处理单元的多个内核以及通信协议处理器和数据信息包传输协处理器,能实现快速无冲突的内部数据传送。

多核共享存储控制器(MSMC)配有DSP内核共享的4 MBSRAM存储器,对共享存储器存取和信息包传输能够并发进行;为了实现对外部存储器快速存取,提供了速度为1 600 MHz的64位DDR3接口,寻址存储空间可达到8 GB。多核导航器配置控制8192个多用途硬件队列的队列管理器,建立基于DMA的零开销信息包传送通道,当需要并行处理的多任务被分配到队列中,多核导航器通过将任务引导到适当的可用硬件来实现任务的加速派遣。网络协处理器支持信息包传送加速和安全加速引擎,增强了与上位机的通信功能。TMS320C6678提供丰富的高速外设接口:四路串行高速IO(SRIO),每路传输速度最高可达到5 GBaud;两通道PCIe—II传输,每通道速度最高可达5 GBa

DSP TMS320C6678 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)