一种单通道DRFM的基带干扰源设计

摘要 通过对单通道数字射频存储器的原理和结构分析,总结了单通道数字射频存储器的优缺点,并基于单通道数字射频存储结构,引入DSP模块设计了一种基带干扰源,实现了对宽带信号的处理。

关键词 数字射频存储器;基带干扰源;数字信号处理

现代新型雷达普遍采用匹配接收和相参信号处理技术,因此具有优秀的目标检测、识别和跟踪能力,同时具有良好抗干扰性能。使用传统噪声干扰信号对相参雷达进行干扰,由于干扰信号不相参,能量利用率低、干扰效果差,迫使噪声干扰机过度提高发射功率,为系统工程实现带来困扰。因此,需要研究相参干扰技术以应对新体制雷达。

数字射频存储器(Digital Radio Frequency Memory,DRFM)利用高速模数转换器件、高速数字逻辑器件进行采样、存储、处理雷达信号,可以产生相参干扰信号。DRFM技术已成为现代干扰技术的核心。

1 单通道幅度量化DRFM的结构及特点

幅度量化是指利用ADC对输入信号幅度进行采样、量化、编码处理,得到数字信号。重构时,数字信号经DAC后输出模拟信号。幅度量化的采样频率和量化位数决定了重构信号的保真度。

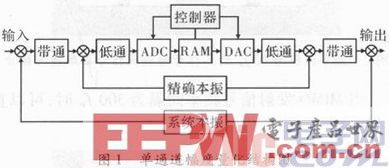

单通道幅度量化DRFM由一路ADC电路组成,其结构如图1所示。工作流程为:输入的射频信号与系统本振进行混频,经带通滤波下变频为中频信号;中频信号与精确本振混频、滤波后,得到基带模拟信号;ADC在采样时钟控制下,实现模数转换,输出数字信号存储到RAM中;在转发过程中,读出数据经DAC、低通滤波后,重构为基带模拟信号;此信号与系统本振混频后,上变频为射频干扰信号。

?

?

假设下变频后输出信号的频率范围为[f0-△B/2,f0+△B/2],为抑制上变频和下变频的高次交调,其中心频率f0与带宽△B之间须满足

2(f0-△B/2)>f0+△B/2 (1)

即

f0>3△B/2 (2)

根据采样理论,采样时钟的频率应满足

fc>2(f0+△B/2)=2f0+△B>4△B (3)

由式(3)可知,单通道幅度量化的采样率应该大于输入信号带宽的4倍。因此单通道幅度量化即便有结构简单、不存在通道幅相不一致问题的优点,但由于ADC器件的限制,存在系统瞬时带宽较小,难以处理宽带信号的缺点。

2 基于单通道DRFM的干扰源设计

为解决宽带信号处理问题而产生的正交双通道DRFM存在幅相要求严格、调试困难的特点,为设计者增加了工作量。随着技术的进步,目前ADC器件的性能有了大幅提高,为采用单通道DRFM处理宽带信号提供了可能。

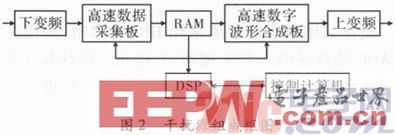

基带干扰源主要完成对基带信号的采集存储、处理分析与基带干扰信号的生成。包括上下变频模块、高速采集板、DSP数字信号处理板、控制计算机和高速数字波形合成器等部分。其组成框图如图2所示。

?

?

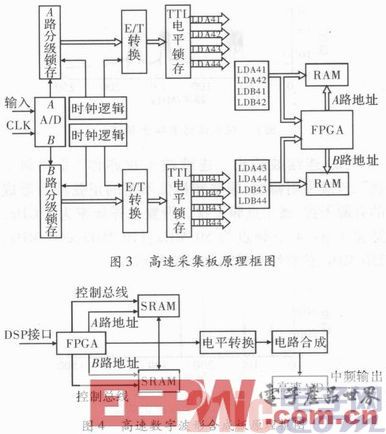

2.1 高速数据采集板

高速数据采集板主要完成模拟中频信号到数字信号的变换,它将中频信号进行量化处理,获得数字信号并存储。干扰源的瞬时带宽要求为400 MHz,采用SPT公司的闪存A/D芯片SPT7760。SPT7760采样率为1 GHz,双路输出,每一路均有锁存时钟,每个端口的输出速度为500 MB·s-1。然后采用ADC输出分为8路的方案,将每一路的数据产生率降为125 MB·s-1,输出存储及处理。由于ADC的输出数据为ECL电平,而

后续的锁存器和缓存器为TTL电平,所以在降速之前选用MICRE公司的SY100系列,将ECL电平转化为TTL电平。

解决高速数据存储的方法一般是在高速数据输入和速度较低的大容量存储器之间加入高速FIFO。由于选择的FPGA与存储器工作频率相同,同为200 MHz。FPGA只需产生同步控制信号在一个时钟周期内将TTL锁存数据存入存储器即可。同时FPGA还完成与DSP信号处理器的接口控制和数据转换等功能。

高速采集板的原理如图3所示。

?

2.2 高速数字波形合成板

高速数字波形合成板实质是高速数字采集器的逆过程,它和高速数字采集器的区别在于它处理的信号是经过.DSP板分析、计算后的干扰信号,其原理框图如图4所示。设计采用Triquent公司的D/A芯片TQ6122。TQ6122是一款高速D/A转换器,转换速率为1GSa/s,具有8位数据位,功耗1.3 W。可广泛用于直接数字频率合成、高速任意波形发生器、宽带视频信号生成等方面。

2.3 DSP处理板

DSP信号处理机用于完成中频采集后信号处理、分析以及干扰样式的产生和部分系统控制的功能。核心处理器由两片组成,两片处理器有独立的存贮器资源,也有相互共享的存贮器资源,它们之间可以独立工作也可以相互通信和交换数据,通信方式为串口通信或通过双口RAM交换数据;DSP还提供数据总线、地址总线和读写信号等控制信号,并与外部高速数字波形合成器的数据接口或高速采集器的数据接口相接,以便交换数据和提供控制信号。DSP处理模块

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)