基于S3C2440的多道脉冲幅度分析器设计

时输出端输出低电平。一旦输入脉冲的峰值到来,则Vin

2.3 控制电路

控制电路的主要实现两个功能:(1)当输入脉冲信号到达峰值后,启动A/D转换器进行转换。(2)精确控制模拟开关J1,和J2的断开和接通,使系统电路以精确的时序工作。

系统的控制电路工作时序图如图4所示,控制电路硬件电路如图5所示。T0时刻是初始状态,模拟开关J1断开,J2导通。T1时刻,输入脉冲的电压高于甄别电路的下限阈值,此时OUTA输出高电平,模拟开关J2断开。T2时刻,脉冲信号上升的峰值,OUTB输出为高电平,启动A/D转换,同时模拟开关J1导通。T3时刻,A/D转换完毕,ARM处理器输出门控信号复位电路,使模拟开关J1断开,J2导通,以迎接下一个脉冲的到来。

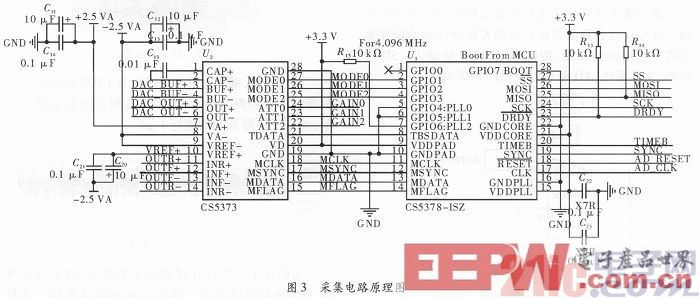

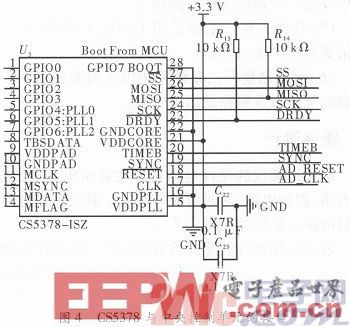

2.4 A/D转换电路

A/D转换器是多道脉冲分析器的核心器件,它对输入脉冲的峰值进行编码转换成为数字量。设计选用美国Burr Brown公司生产的低功耗CMOS工艺逐次逼近型的A/D转换芯片ADS774。ADS774采用单一的+5 V电源供电;典型功耗120 mW;非线性误差±1/2LSB;转换速度为8.5 μs,能较好地满足设计需要。

A/D转换电路图如图6所示。核脉冲信号从峰值扩展电路输出后进入ADS774的BIP OFF引脚进入转换器。R/C引脚连接控制电路,该引脚输入低电平信号可以启动A/D转换,输入高电平信号时,CPU读取转换结果。STS引脚反映了A/D转换的状态,转换过程中,输出高电平。转换结束后,STS引脚输出低电平。A/D转换结束后,STS引脚发出下降沿有效的中断请求给CPU。CPU收到中断请求后,在中断处理程序中读入转换结果。为进一步提高A/D转换结果的精度,降低道宽的非线性误差,只使用了12位转换结果的高10位,舍弃了最低两位的转换结果。因此,只把ADS774数据线的DB2~DB11接入系统数据总线。

3 系统测试

系统电路板制作完毕后,首先进行输入电压的幅度-道址对应关系测试。使用精密信号发生器产生不同幅度的脉冲信号,直接对多道脉冲幅度分析器的A/D转换结果进行测试。输入信号幅度范围0~5 V,先输入幅度值较小的脉冲信号,重复进行若干次的测量,通过LCD显示屏观察本幅度脉冲所对应的道址。以脉冲信号的信号幅度为横坐标,对应的道址为纵坐标,得到如图7所示的曲线。将其采用最小二乘法进行拟合,得到道址与幅度之间相关系数R2=0.999 4,两者之的关系式为:y=201.98x+13.361。这表明,本系统具备良好的线性。

本系统A/D转换器ADS774的实际测量结果与理想转换函数值的最大误差为±1/2LSB,因此系统的积分非线性(INL)为±0.37%,微分非线性(DNL)接近于0。使用精密信号发生器对幅度值为4.5 V的信号行连续8 h的测量,每小时记录一次道址,测量数据如表1所示,这表明,系统的峰位漂移<2%,具备良好的稳定性。

4 结束语

S3C2440处理器具有32位的总线宽度和1.1 MIPS/MHz的指令处理速度,可以满足对时间要求非常苛刻的事件的快速实时处理。此外,S3C2440处理器丰富的外设接口也使得整个设计更加便捷。测试表明:设计达到了1 024道的多道脉冲幅度分析器硬件要求,具备良好的微分非线性和积分非线性,系统分辨率高、工作稳定性好。此外,由于系统硬件采用了集成度高、功耗低、贴片式的元器件,因此系统体积小、携带方便、操作灵活、可以应用于实际工作中。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)