基于FPGA和AD1836的I2S接口设计与实现

=~LR_f; //左右通道时钟

BCLK_f=1'b1;end //送出位数据时钟

2: datout=DDSdatin[23];//送出最高位

3: datout=DDSdatin[22]; //送出次高位

4: datout=DDSdatin[21];

5: datout=DDSdatin[20];

6: datout=DDSdatin[19];

7: datout=DDSdatin[18];

8: datout=DDSdatin[17];

9: datout=DDSdatin[16];

10: datout=DDSdatin[15];

11: datout=DDSdatin[14];

12: datout=DDSdatin[13];

13: datout=DDSdatin[12];

14: datout=DDSdatin[11];

15: datout=DDSdatin[10];

16: datout=DDSdatin[9];

17: datout=DDSdatin[8];

18: datout=DDSdatin[7];

19: datout=DDSdatin[6];

20: datout=DDSdatin[5];

21: datout=DDSdatin[4];

22: datout=DDSdatin[3];

23: datout=DDSdatin[2];

24: datout=DDSdatin[1];

25: datout=DDSdatin[0]; //数据已经发送完毕

26: datout=0; //剩余的数据送0

27: datout=0;

28: datout=0;

29: datout=0;

30: datout=0;

31: datout=0;

32: datout=0;

default:datout=1'bz;

endcase

end

软件仿真

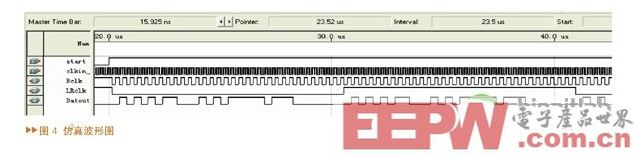

模块的仿真也是在软件QuartusⅡ6.0中实现的,仿真波形如图4所示。为了便于仿真,在24位的并行数据输入口输入十六进制的常数 AB15F7H,此时送入左右通道的数据是相同的。从仿真波形中可以看出,当start信号高有效后,位数据时钟和左右通道数据切换时钟送出,将并行的 24位数据AB15F7H从数据线上串行送出,在多余的位数据时钟处数据线上的数据为0,仿真结果与I2S接口时序图相符合。

?

?

结束语

本文以FPGA为控制单元,完成了AD1836中D/A部分的I2S接口设计,它在数字音频系统的设计中有一定的参考和实用价值。该设计已经成功运用在某话路特性综合测试系统中,性能良好。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)