基于FPGA的北斗QPSK信号调制器设计

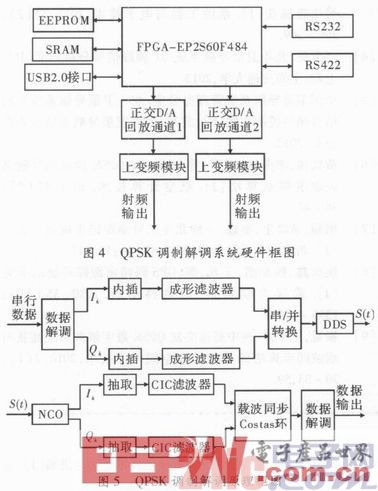

框图如图4所示,系统原理方案如图5所示。

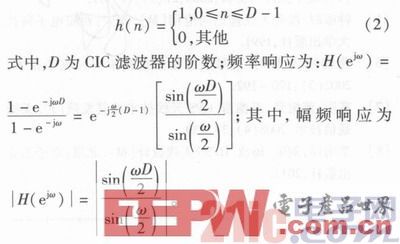

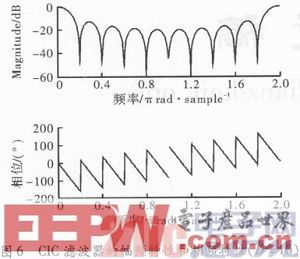

图5中CIC滤波器即级联积分器梳状(Cascade Integrator Comb,CIC)滤波器,滤波器的冲击响应如下形式

调制部分,数据通过串口输入,产生宽度为8 bit的并行数据流,然后分成I,Q两路数据流,经过补零内插,成形滤波和数据位截短后,通过并串转换,再通过DDS模块生成基带QPSK调制信号。调制输出数据的速率是128 kbit·s-1,而实现DDS的器件AD9857中设定输入数据速率是1 Mbit·s-1,为使两者速率匹配,设计中采用内插方法来实现。在内插模块的设计中,采用最简单的实现方法,即在数据之间插零。零的个数N由内插前后数据的速率决定,设计中N=7。内插模块通过数据锁存器和计数器实现。在内插模块设计中,由于采用了“插零”处理,导致码间干扰和带外辐射增大,为减小这些对信号解调的影响,设计采用成型滤波器。并串转换模块通过4级锁位寄存器实现,并行16位的输人数据按照并行4位的格式串行输入到DDS。

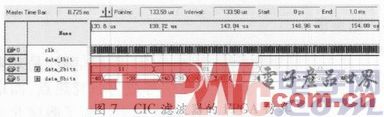

在解调部分,通过NCO进行数字下变频,经过抽取,CIC滤波器进行滤波,Costas环进行载波同步,最后解调处数据,通过串口输出显示。数字下变频模块主要由NCO和混频器组成。混频器为8位乘法器,采用Ahera提供的宏功能模块LPM_MULT,将数据锁存模块输出的8位数据与分别NCO输出的正交载波进行相乘,乘积结果为一有符号的16位数据。为防止乘法器输出数据在后面模块运算处理中发生溢出,同样在设计中对数据进行了截短处理。CIC滤波器采用三级8倍抽取的积分滤波器与梳状滤波器并联。Costas环来估计和校正解调过程中的多普勒频移。

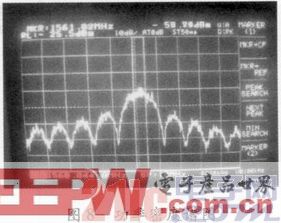

在测试部分,串口输入数据是1234FA42342343,串口输出12 34 FA 42 34 23 43,说明了QPSK调制解调系统的正确性。同时,通过频谱仪对设计的QPSK调制信号进行观察,FPGA开发板射频端口输出1 561.020 MHz的射频信号,证明生成的QPSK调制信号在频率特性、频谱特性上符合系统设计要求,从而证明了调制信号的正确性,功率密度谱如图8所示。

5 结束语

北斗卫星导航系统,特别是B1频段信号,是未来民用的主要信号,因此,频段信号成为研究热点,而市场对北斗接收机的需求也会越来越多。为了测试北斗卫星导航接收机的性能,则需要模拟北斗卫星导航系统在各种环境下的真实卫星信号。本文针对北斗信号QPSK调制信号的结构特点,分析了QPSK调制解调的原理,并结合软件无线电的方法,通过FPGA验证了系统的可行性和正确性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)