基于DSP的图像压缩系统设计

引言

随着多媒体和网络技术的发展,数字图像大信息量的特点对图像压缩技术的要求越来越高,因此,专用高速数字信息处理技术成为发展的方向。TI推出的C5000系列DSP将数字信号处理器使信号处理系统的研究重点又回到软件算法上。在压缩算法研究方面,DCT、小波等多个算法因为其高可靠性和高效性也越来越受到青睐。

系统硬件设计

TMS320C5409作为主处理器的可行性分析

TMS320C5409时钟频率为100MHz,性价比极高。采用围绕1组程序总线、3组数据总线和4组地址总线建立的改进型哈佛结构,取址和读数可同时进行。有独立的硬件乘法器,有利于实现优化卷积、数字滤波、FFT、矩阵运算等算法中的大量重复乘法运算。具有循环寻址、位倒序等特殊指令,这些指令使FFT、卷积等运算中的寻址、排序及计算速度大大提高。有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作。

在本系统中,TMS320C5409作为主处理器,任务是实现JPEG压缩编码。

通过分析不难得到,当处理一帧大小为640×480的图像时,作JPEG压缩编码所需要的时间为:T=62×10(ns)×640×480=0.19866s,当所处理的图像分辨率更小时,则压缩每帧所花的时间更少,这对于应用在对实时性要求不是很高的场合是完全可行的。

图1是基于TMS320C5409的图像处理系统结构图。C5409为中央处理器,SRAM为DSP片外扩展数据存储器,EEPROM为脱机工作时的程序存储器,用于存储系统的引导程序和其它应用程序,A/D转换部分负责把转换为数字信号的图像存入帧存储器中。地址译码、图像采集系统控制电路产生本系统各部分的地址译码信号,使之映射到不同的地址区域,并控制ADC进行图像采集,这部分由CPLD控制;图像采集芯片的寄存器控制由51单片机完成。

存储空间的扩展方案

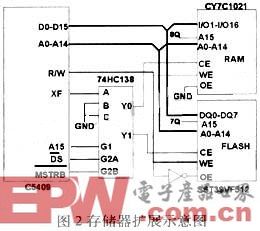

经过A/D转换的原始图像数据是非常大的,TMS320C5409的内部仅有32KB的RAM和16KB的ROM,不能满足需要,因此,必须扩展存储器来存放原始图像数据和应用程序。本文考虑外接64KB的RAM和512KB的Flash,RAM使用Cypress公司的CY7C1021V33,Flash采用SST公司的SST39VF512.由于C5409的数据空间仅为64KB,因此采用内存页扩展技术。C5409的扩展输出口1Q和2Q作为扩展内存的页选择信号。用C5409的A15引脚和XF引脚通过3/8译码器来控制扩展存储器片选信号的产生,当A15=0时,选择片内RAM;当A15=1,XF=0时选择片外SRAM;当A15=1,XF=1时选择片外Flash;存储器的扩展如图2所示。将外部扩展RAM的64KB中的48KB用于存放原始图像数据,16KB用于存放压缩后的图像和程序以及暂存的数据。

DSP芯片电源电路设计

电源设计中需要考虑的主要问题是功率和散热。功率要求:电流的消耗主要取决于器件的激活度,即CPU的激活度,外设功耗主要取决于正在工作的外设及其速度,与CPU相比,外设功耗是比较小的。以TMS320C5409为例,进行FFT运算时,需要的电源电流最大。因此在设计电源时,必须考虑在电源电流和实际需用电流之间留有一定裕量,因为峰值电流会更大,裕量至少是20%.

C5409采用了双电源供电机制,工作电压为3.3V和1.8V.其中,1.8V主要为DSP的内部逻辑提供电压,包括CPU和其它所有外设逻辑。外部接口引脚采用3.3V电压。本系统的电源采用了TI公司的两路输出电源芯片TPS73HD318,它是一种双输出稳压器。输出电压一路为3.3V、一路为1.8V,每路电源的最大输出电流为750mA.

JPEG图像压缩算法

JPEG算法的优化

尽管JPEG基本系统能够对图像进行低压缩比压缩,但是DCT和IDCT在软件实现的过程中,是最耗费时间的运算,而且,由于没有考虑图像本身的频谱特性,JPEG量化表对于所有图像压缩并不一定最优。采用快速DCT算法可提高软件的速度,增强软件的实时性。同时,根据图像本身的频谱特性,自适应改进JPEG推荐的量化表。

快速DET算法

如果将一幅图像分成许多8×8的小块后直接进行2D-DCT变换,运算量将会十分巨大。因此,需要将8×8二维DCT变换转换成两次8点的一维DCT复合运算。具体做法是对每一个8×8块先做列方向上的DCT变换,得到一个中间矩阵,再对该矩阵各行进行DCT变换。可以看到,8×8矩阵的2维DCT可以转换成16次一维8点DCT.

目前,很多针对一维DCT运算的DCT快速算法已经提出。其中,Loeffler算法所需要的计算量最小。Loeffler算法将8点一维DCT运算分为4级,由于各级之间的输入/输出存在依存关系,4级操作必须串行进行,而各级内部的运算可并行处理。

流程图中有三种运算因子:蝶形因子、旋转因子和倍乘因子,分别如图3中的a,b,c所示。蝶形因子的运算关系为:

D0=I0+

- Linux标准趋向统一(11-12)

- 巴西的新电视机顶盒采用意法半导体(ST)的最先进的解码器技术(03-24)

- 基于TMS320C62X DSP的混合编程研究(07-12)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 展望未来 多核DSP技术不仅仅是小把戏(04-03)

- 嵌入式软件工程师必须知道的:volatile的作用(05-01)