一种高速DSP与PC串口通信的设计方案

帧同步信号后开始接收数据,并不再考虑FSR信号,在一帧信号传输的最后一位时,FSR必须为低电平,否则将会被作为下一帧的帧同步信号位。

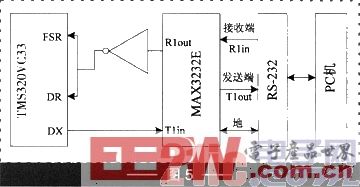

TMS320VC33微处理器与标准串口间的通信硬件结构如图5所示,同样采用三线连接的电路。因PC起始位为低电平,TMS320VC33微处理器帧同步位为高电平,为使两者统一,MAX3232E的R10ut信号经一反相器后,再连接到DSP的DR和FSR引脚,同时加反相器后,数据相位和停止位都相应变反,但是很容易用软件方法还原数据信号。

2.软件设计

软件设计比前两种方法更为简单,只需将串口的相应寄存器位设置好,然后开启相应中断即可完成与PC的通信,此方法在接收时采用帧同步信号,误码率较低,是一种比较实用的方法。

①在DSP接收时,接收信号同时连接到接收引脚DR和接收帧同步引脚FSR,故PC发送1帧信号的起始位是被用作接收帧同步信号,然后才开始接收数据,而且FSR引脚在接收帧的最后一位时必须为低电平,以满足TMS320VC33微处理器爆发方式串行通信的要求。PC采用上述发送帧格式,停止位反相后,正好满足FSR的要求。

②在DSP发送时,微处理器的字长只能是8、16、24或32位,且不需要起始位、结束位;RS232的字长只能是8位,且需要起始位和结束位。由图5知,TMS320VC33微处理器的FSX采用内部同步,DX引脚上为数据位,为符合PC接收的帧格式,需将数据位设置为16 位,将最高位作为起始位、8位数据位、1位停止位、6位空闲位,即符合PC帧格式为10位的通信要求,同时空闲位不影响数据通信,同时也正是由于有空闲位,所以采用固定速率的爆发方式。

结论

本文的TMS320VC33微处理器与PC实现串口通信的方法可以为其它型号的高速DSP与PC之间实现通信提供参考。

另外,将MAX3232E芯片换成MAX485可实现DSP与RS-485接口的通信,即提高了数据传输速率,增加了传输距离,同时,增强了数据传输中抗干扰能力,对复杂环境的数据传输通讯有重要的应用意义。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)