基于DSP的以太网通信接口设计

4 调试结果

根据以上设计,笔者在原TM1300视频编码硬件系统的基础上加入了PCI接口,并编写了pSOS下Realtek8029的驱动程序。然后,在这个硬件平台上对Realtek8029的驱动部分进行了数据传送测试。 笔者首先用一个单独的UDP发送任务进行发送速率测试。这个任务主要是高速地向网络上的一台PC发送数据包,数据包的大小是变长的。PC接收并对丢包数进行统计的结果如表1所列。实验表明,在用网线直连的各种测试速率情况下都没有出错,而当接入局域网后,在发送速率为4.5Mbps时有突发的少量错误。由于UDP是不可靠的传输方式,所以这种错误是正常的。测试中,UDP发送的最高速率可以达到5Mbps左右,它与硬件的最高速率(10Mbps)相比还有一定差距,主要原因是数据从系统主内存到Realtek8029片上RAM的拷贝过程目前尚未采用DMA方式,这是需要改进的地方。 表1 丢包数统计表(单位:丢包个数/分钟) 连接方式发 送 速 率 800kbps 1.8Mbps 4.5Mbps 网络直连 0 0 0 接入局域网 0 0 2.5 接下来笔者进行了编码和传送的联合测试。编码任务执行H.263数据压缩后,把码流从以太网接口发出,然后在网络上的另一台PC上接收这个码流,并进行解码播放。通过调整编码器的量化步长可以控制编码的输出码率。在实验环境下发现在量化步长大于等于5、码率在700kbps以下时,基本没有丢包现象,解码得到的图像比较稳定,而当量化步长进一步减小,码率接近1Mbps时,就会出现丢包现象,解码的图像会出现彩色方块。出现这种现象是因为H.263编码器对CPU资源的消耗很大,而且数据在主内存和Realtek8029片上RAM之间的复制采用I/O读写方式也需要一定的CPU资源。这样,当量化步长小于5时,处理的复杂度超过了CPU的能力从而产生了一定的误码。解决的途径一方面是改进数据的传送方式(采用DMA),另一方面是需要对编码任务进行优化。

5 小结

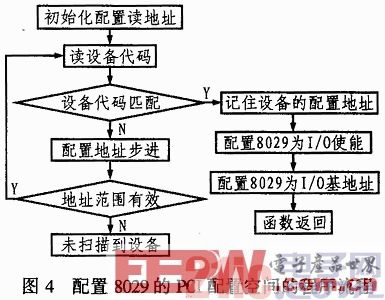

本文介绍了PCI总线接口的设计以及PCI空间初始化的步骤,同时对测试结果进行了较详细的分析,提出了以后改进的方向。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)