基于MS320C6678的多路同步时钟信号设计

现无缝连接。

3 硬件设计

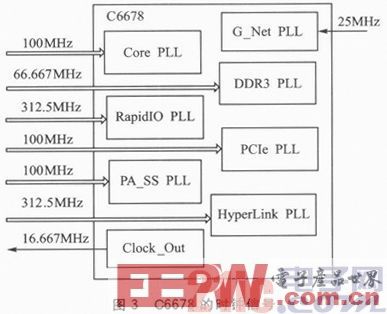

根据TMS320C6678的应用,所需要的时钟如图3所示。

其主要时钟包括:①内核运行时钟,该时钟输入是100 MHz,DSP片内PLL将其锁定到工作频率,最高为1GHz,最低为700 MHz。②RapioIO接口和HyperLink超级连接接口工作时钟,这两路时钟输入都为312.5MHz,RapioIO倍频4、8、10、16,工作在1.25 GHz、2.5GHz、3.125 GHz和5 GHz。HyperLink倍频到40、80、100、160,工作在12.5 GHz、25 GHz、31.25 GHz和50 GHz。

③PCIe接口时钟和PA_SS网络加速器时钟,这两路时钟都是输入100MHz,内部倍频后相应的工作时钟,满足各自接口传输时钟要求。④DDR3时钟,该时钟输入为66.667 MHz,倍频20或者25倍,工作在1333.33 MHz或者1666.7 MHz。这些时钟在DSP片内都各有独立的PLL电路设置,其工作原理和设置方法基本一致。图3中的单独25 MHz是专门为千兆网提供的工作时钟,由一个单独的晶体提供。C6678还提供一路时钟输出信号,默认输出为核时钟的1/6,图中为16.667 MHz,输出时钟可以检测C6678是否正常工作。

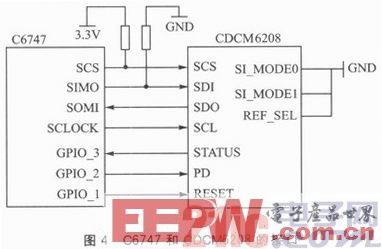

由于C6678的核时钟由CDCM6208提供,所以对CDCM6208的设置只能由另外一个处理器完成,只要该处理器具有SPI或者I2S接口即可。本文使用低功耗的DSP芯片C6747来实现多CDCM6208的设置。C6747和CDCM6208的接口如图4所示,采用标准4线制SPI接口控制,为了避免干扰提高传输可靠性,在SPI的片选信号的写信号分别上拉和下拉,这样在空闲下其引脚状态不会被干扰。在控制CDCM6208之前,需要对其进行复位,图中使用一个通用GPIO引脚控制,当CDCM6208配置成功后,会提供一个状态检测信号,该信号连接到C6747的GPIO引脚,用来判断是否正确配置。图中C6747还使用一个引脚控制CDCM6208的低功耗设置,当该引脚为高时,CDCM6208进入低功耗模式。

4 软件设计

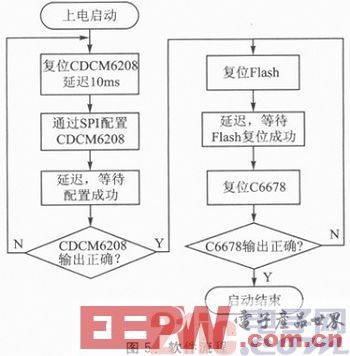

由于系统采用C6747控制CDCM6208时钟信号,所以C6747的软件是系统整个初始化的关键,C6747的初始化软件主要包括对CDCM6208的复位、配置和检测以及对C6678的复位、C6678外挂Flash的复位等工作。整个系统的软件流程如图5所示。

上电启动后,C6747软件加载成功后,复位CDCM6208,为确保复位成功,C6747要等待10 ms才能通过SPI接口配置CDCM6208。配置完成后,C6747可以查询CDCM6208的状态输出引脚,检测是否配置成功。如果配置失败,重复复位、配置、检测这几个步骤。配置成功后,表明CDCM6208已经输出准备时钟到C6678,但在此之前,C6678仍然处于复位状态。由于C6678的程序保存在片外Flash中。所以,C6747要首先复位Flash,等待其复位后,再复位C6678,查询C6678的输出状态,确定C6678是否正常下作。如果输出不正常,仍然重复复位Flash、复位C6678和检测这几个步骤,直到初始化成功。

结语

多核处理器由于其接口丰富,运行频率较高,对时钟设计要求较高,一般要求一个高精度的时钟通过分频/倍频方式产生多路时钟到相应的接口。本文以多核数字信号处理器C6678为应用对象,通过CDCM6208产生多路时钟,提供到多核DSP的核时钟、DDR3、RapidIO等时钟信号。通过单核低功耗小成本处理器C6747实现对整个时钟电路的复位、设置和检测。本文介绍的时钟配置方法具有通用性,对同类产品的时钟设计方案具有一定的参考价值。

DSP MS320C6678 同步时钟 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)