基于嵌入式NiosⅡ的SD卡驱动设计

近年来,基于FPGA的软核处理器以其高度的设计灵活性和低成本在嵌入式市场中得到重视并不断发展。其中具有代表性的软核处理器有Ahera的 NiosⅡ处理器和Xilinx的MicroBlaze处理器。NiosⅡ处理器具有完全的可定制性,包括处理器的定制,外设的定制和接口的定制等;32 位的NiosⅡ处理器具有超过200 DIMP的性能,而其成本只有同级别性能ARM处理器的l/10。此外,SD存储卡以其大容量和小尺寸的特点,成为市面上各种嵌入式消费产品最常见的存储媒介,探讨SD卡设备的设计具有广泛的应用价值。这里将结合NiosⅡ处理器的总线架构,分析SD卡的接口协议和驱动程序设计方法,并给出SD卡设备在NiosⅡ处理器的设计实例。

1 NiOSⅡ处理器的Avalon总线架构

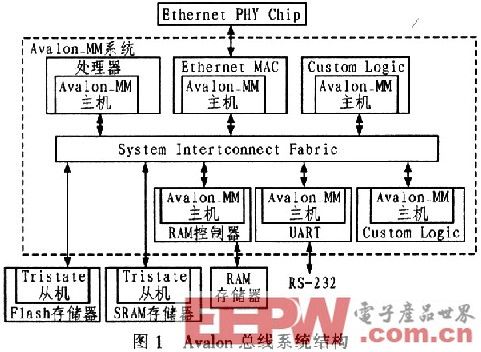

Nios和NiosⅡ都使用了Avalon总线,这是一种交换式架构的片内总线。该总线形式和PCI、ISA等板间互连总线的最大区别在于:其主从设备之间有紧密耦合关系。Avalon总线架构中,由硬件设计人员通过SOPC Builder规定互连的主从设备(包括数据、控制信号、片选、地址的互连),不连接的设备之间是互相看不到的。每个Avalon主设备端有多路复用器,用来从多个从设备的数据总线中选择当前要访问的数据。图l为Avalon总线系统结构。

Avalon接口用于提供描述主外设和从外设中基于地址读/写接口的基础,例如,微控制器、存储器、UART及定时器等。接口规范定义了外设和 Avalon开关互联结构之间的数据传输。在没有主或从接口限制的情况下,规范的互联策略允许任何主外设连接到任何从外设;Avalon接口描述了一个可配置的互联策略,允许外设的设计者限制某种特定传输所需的信号类型。

Avalon定义了5种传输方式:从端口传输、主端口传输、流水线读传输、流传输控制和三态传输。这里仅分析SD卡设备所使用的从端口传输方式。

1.1 从设备信号

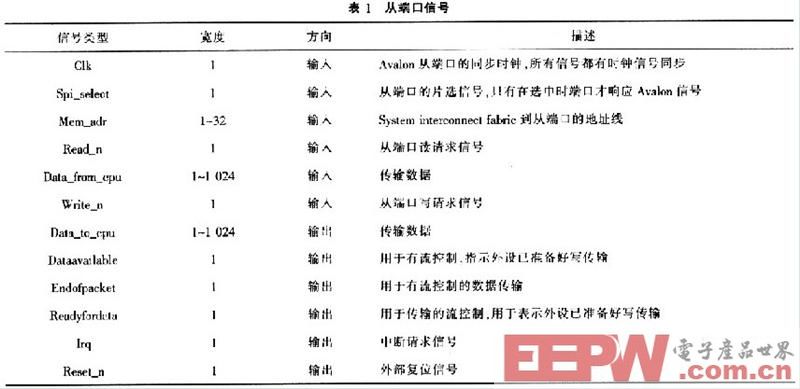

从设备信号是与主设备相连接的一组信号端口,这里所针对的SD卡设备的Avalon从端口需定义的信号端口如表1所列。

表l所列出的从设备信号只是这里所针对的SD卡设备所需要的信号,并不是从设备所支持的所有信号。对于其他从设备可根据其自身特点及需要来选择相应的信号接口。

1.2 从端口读/写传输

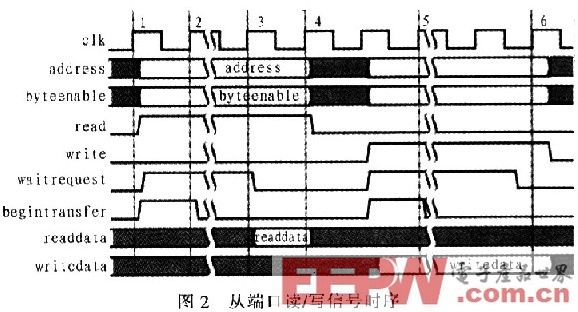

从端口读传输是主设备通过SD卡控制器对SD卡进行读取的操作,即读取SD卡的数据;从端口写传输是主设备通过SD卡控制器对SD卡进行写操作,即对SD卡写入数据。图2为从端口读/写信号时序。

从端口读传输时,在时钟上升沿开始传输数据,并在下一个时钟上升沿完成传输。在clk的第1个上升沿,systeminterconnect fabric配合read、begintransfer信号将有效的address,byteenable和read信号传输给从端口,且system interconnect fabric在内部将address译码,产生并驱动从端口的chipselect信号。chipselect信号一旦有效,则从端口立即驱动 readdata。system interconnect fabric则在下一个clk上升沿捕获readdata。

从端口写传输是由system interconnect fabric发起的。它向从端口传输1个单元的数据,且在1个时钟周期内完成。system intercon-nect fabric配合write、begintransfer信号提供address,writedata,byteenable和write。system interconnectfabric不对address进行译码,驱动chipselect,并使其有效。从端口在下一个时钟的上升沿捕获地址、数据和控制信号,并完成写传输。

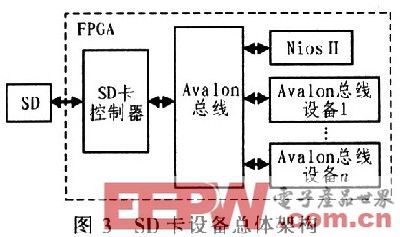

从端口的读写时序是通过SD卡控制器完成的,而SD卡的控制器是以NiosⅡ软核处理器外设的形式与处理器相连接的。其关系如图3所示。

2 SD卡的接口协议分析

SD卡即可靠数字存储卡(Seeure Digital Memory Card),是为满足消费电子类产品对安全、容量、性能等有特殊要求的环境而设计的。 SD卡定义了SD和SPI这2种可选择的总线协议。这里研究的是SPI协议下的SD卡设备开发。SPI是面向字节的传输,SPI的命令和数据块都是以8个比特为单位进行分组的。SPI的信息分为控制帧、反馈帧和数据帧,所有的SPI信息都是建立在命令、应答和数据端口标记上的。所有主机和卡之间的通信都由主机控制,主机通过拉低CS信号开始一个总线事务。

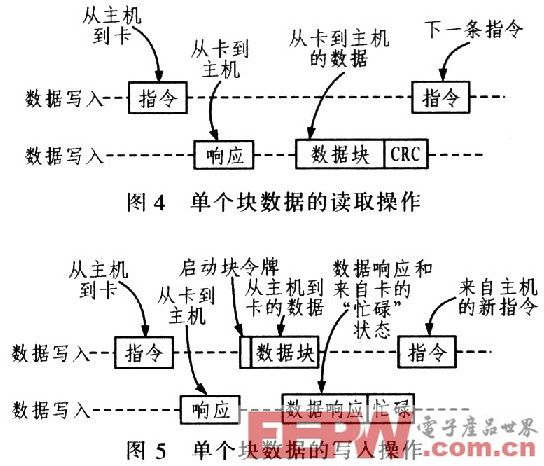

SPI模式下,SD卡可支持单个块和多个块的读/写操作,在接收到一个合法的读取命令后,这个SD卡可将用一个应答标志来应答响应,随后的就是一个数据块。在接收到一个合法的写指令时,SD卡将响应一个应答标记,并等待主控制器发送这个数据块。图4为单个块数据的读取操作,图5为单个块数据的写入操作。

3 SD卡驱动设计

NiosⅡ软件架构是建立在硬件抽象层HAL(Hardware Abstraction Layer)之上的,HAL为Nios软件开发者提供了编程接口、

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)