基于多DSP的在线可重构数字图像并行处理系统设计

算法的需求,使算法执行效率达到最高。静态重构和动态重构使系统相比传统固定系统具有很强的通用性和适应性。

②系统的“多DSP+FPGA”结构能将系统任务划分成适合FPGA处理的低层信号处理和图像预处理部分及适合DSP处理的算法,便于发挥两者的优势;且FPGA可通过软件适应不同时序格式的数字图像,使得系统具有很高的性能和灵活性。

3 系统设计实例

3.1 系统硬件结构

基于TI公司C6000系列DSP和Xilinx公司Spartan一3系列FPGA,构建基于图像的点源目标识别系统,对在线可重构数字图像并行处理系统的可实现性和性能进行验证。

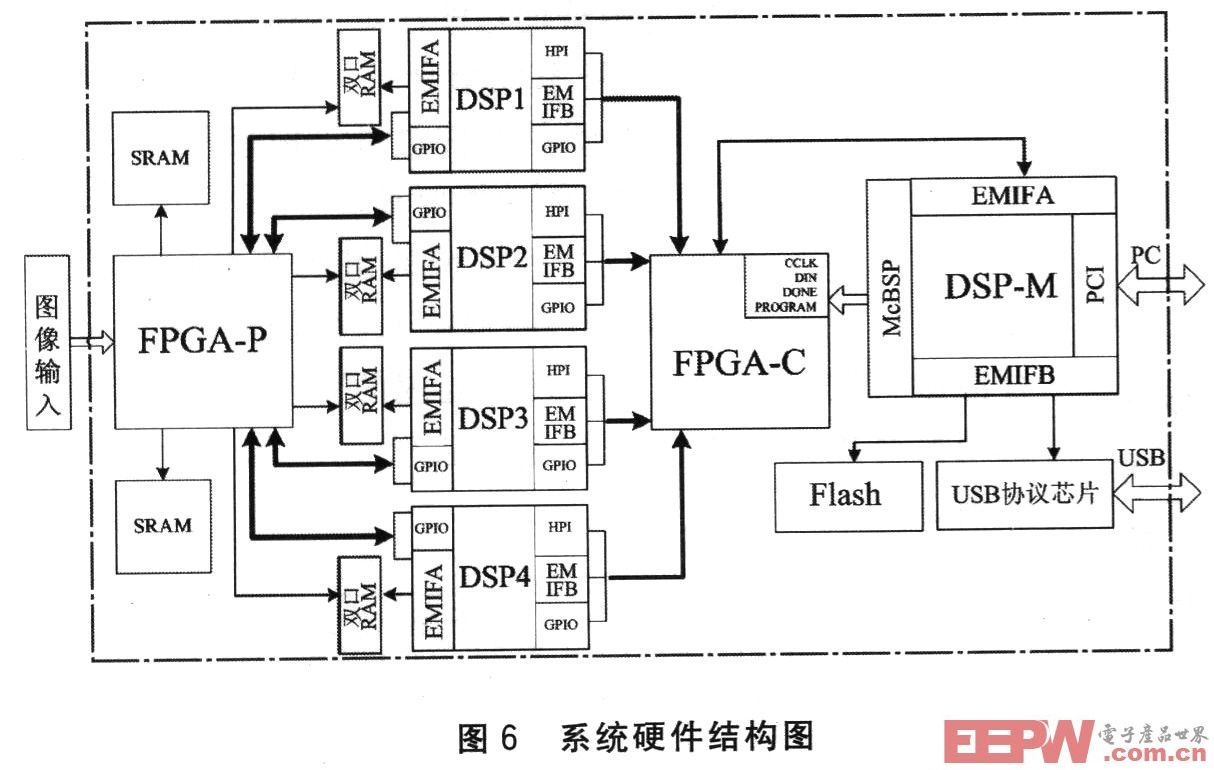

硬件结构如图6所示。图像输入FPGA—P,各DSP分别外扩一片双口RAM,且将总线EMIFA接到FPGA—P。FPGA—P可用来完成图像时序处理、图像数据的转换、图像滤波等预处理工作,且可以灵活地将处理后的图像数据保存到大容量公用数据存储器SRAM中,并将各DSP访问的仲裁逻辑或分配保存到各DSP外扩的双口RAM中。这种结构使系统可以轻松地适应多路图像输入。

DSP阵列可以并行完成各种图像处理算法。FPGA-C建立起DSP间的通信链路且暂存各DSP的处理结果。构建通信链路的方法有:用FPGA—C在两 DSP之间构造FIF0或小容量双口RAM,构建EMIF—HPI通路等。DSP-M可以根据算法需求通过McBSP在线配置FPGA—C,FPGA—C 的配置文件存放在DSP—M外扩的Flash中,这样就实现了DSP对FPGA的在线可重构。同时,DSP-M扩展了USB、PCI、McBSP等多种接口用来输出图像处理结果。

3.2 实验及结果分析

系统用于实现4路分辨率为256×256、帧频为50 Hz的8位图像(如图7所示)的移动点源目标识别。

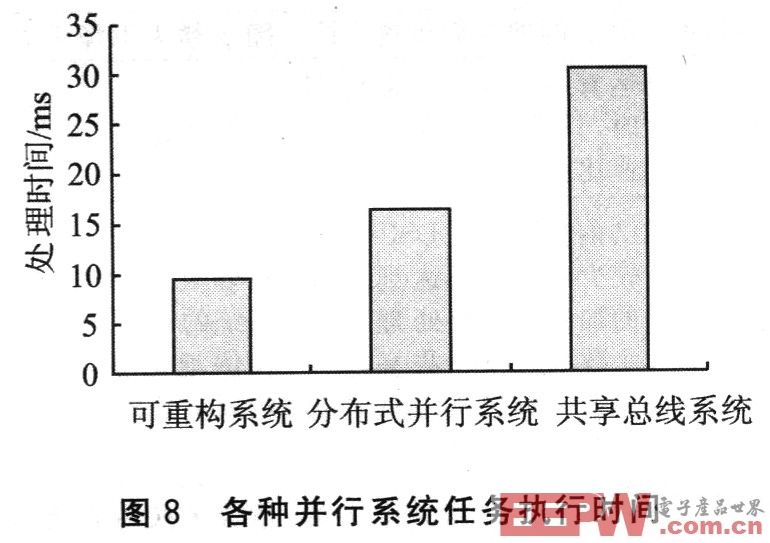

处理过程包括图像时序采集、转换,图像滤波,去除噪声,姿态融合和目标识别等环节。图像分配和算法执行所需平均时间仅为9.5 ms。

若用共享总线系统来实现,则多路图像数据的存储和分配以及处理器之间的通信将消耗大量时间,大大降低系统效率。若用分布式并行系统来实现,则姿态和多路图像的综合处理会给某一个处理器带来很大的通信量和运算量。将实验中的图像处理任务在同等规模的3种系统上分别实现,执行时间如图8所示。

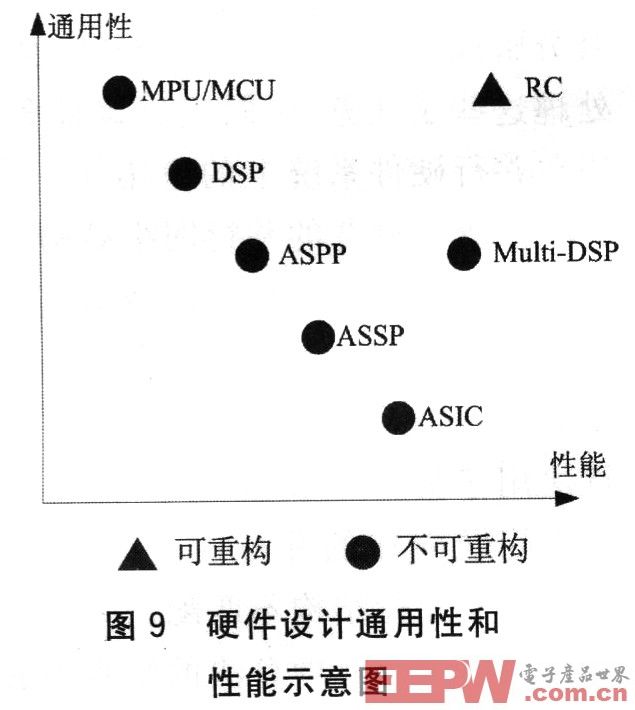

如图9所示,这些不同形式的计算系统是性能和通用性的不同折衷。可重构算系统代表了介于ASIC和通用处理器之间的计算途径,在通用性和性能上都优于传统的硬件系统。图像处理中数据量大、算法复杂,与其他计算技术相比,可重构计算能充分发挥出效率优势。可重构系统具有很多优点,但重构延迟和软硬件划分问题是应用中需要重点考虑的问题。

结 语

传统固定结构并行图像处理系统不能适应多种图像处理并行算法。而可重构数字图像并行处理系统数据流和结构组织灵活,适于模块化设计,能大大提高并行算法的执行效率;有较强的通用性,同时其开发周期较短,易于维护和扩展。可重构数字图像并行处理系统为多媒体图像处理提供了一个非常有价值的发展方向。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)