FPGA研发之道—总线

。(即回环这种设计与处理器的cache结构是相关的,现在的cache line有逐渐扩大的趋势,一般64字节也较为常见)。

由于支持多个主设备和多个从设备进行交互,那么对于多个主设备之间就存在竞争。(从设备之间存在竞争否?从设备之间是通过地址区分的,被动接受主设备的访问,不会存储竞争的问题。)因此如何解决竞争,那就需要仲裁,即主设备谁需要访问总线,则发起HBUSREQ,而仲裁器收到HBUSREQ,返回给相应主设备HGRANT。此时该设备才能访问总线。除此之外AHB还有其他一些信号,用于辅助整个系统的传输,感兴趣的同志,可以看一下AMBA的总线规范。值得一提的是,作为一个总线规范,其提供了全集的解决方案,而作为实现部分,只需要在满足规范的前提下,实现必要的功能即可,例如AHB总线中规定,其突发最大可1K字节,但是作为一个从设备,不一定需要支持这么大的操作,即实现功能可在总线框架内进行裁剪,选择实现支持的类型即可。

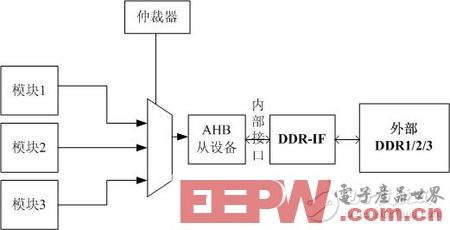

在FPGA内部设计中,经常有多个主设备访问同一从设备的例子,例如内部多个模块都需要访问外部存储器,其实现方式有多种,通过AHB的连接架构,可以实现一个标准、可扩展的接口单元,用于访问外部存储器。并且可以作为IP使用。AHB从设备只需要根据需要,支持某些burst传输即可。

随着SOC(片上系统的发展),对于高带宽、低延时的总线需求更加迫切,ARM公司适时退出AXI(AMBA3.0)作为扩展。

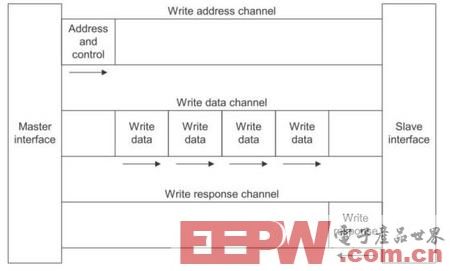

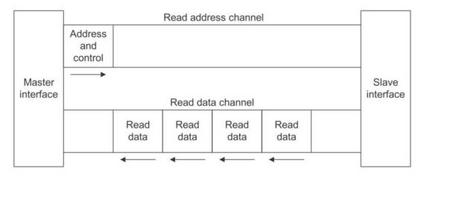

上图分别是AXI接口的读写操作,分别可以看出,对于AXI总线来说,其有5组独立的总线,分别是写地址,写数据,写响应,读地址,读数据信号。地址和数据信号分开,每组都有自己的控制信号。

每个通道中间没有时序关联,如何进行操作的?举例来说明,例如读数据操作,实际上,主设备向从设备中写了一个读的命令,包括读地址,burst大小,方式等。收到后从设备按照相应的命令读取相应大小的数据,传回主设备,其操作可以简化的看做两个缓冲区类型的操作,主设备将读命令写入从设备的命令缓冲区,从设备取出后,根据命令将相应的数据返回给主设备的接收缓冲区中。这种操作的好处显而易见,能够最大限度的减少总线的开销,因此其读与读操作之间独立,不用等待读回,就可以发送下一次的读信号。写操作的流程亦然。

对FPGA设计来说,例如xilinx的接口IP(DDR例化时的接口),都已支持AXI的接口。FPGA工程师熟悉相应的总线接口信号和特点,对于技术方案选择,IP使用和验证,都是非常重要的。尽量在设计中选择标准总线接口,对于设计复用,模块共享来说,则是必由之路。而模块(IP)复用的益处随着设计不断增大将会不断显现。

FPGA AVALON-MM AVALON-ST 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)