FPGA复位的可靠性设计方案详解

如下:(1)异步复位的作用和释放与时钟沿并无直接关系,异步复位生效时问题并不明显;但当释放异步复位时,若异步复位信号释放时间和时钟的有效沿到达时间几乎一致,则容易造成触发器输出为亚稳态,形成逻辑错误。(2)若异步复位逻辑树的组合逻辑产生了毛刺,则毛刺的有效沿会使触发器误复位,造成逻辑错误。

2.3 外部复位和内部复位

外部复位,复位信号主要来自外部引脚的输人。复位信号在电路板上可能会受到来自其他线路的串扰,因此可能产生毛刺,在无需复位系统时,毛刺信号可能导致系统误复位。

内部复位,FPGA上电配置完成后,由FPGA内部电路产生复位信号,复位信号与时钟同步。通常内部复位的设计方法是:设计一个初始值为0X0000的SRL16,将其输人接高电平,输出作为复位信号。

3 复位可靠性设计方法

3.1 消除复位信号上的毛刺

在系统设计中,若采用低有效复位信号,可按照图3所示方法对复位信号中的毛刺进行消除。延时器件对数据进行延时的长度决定复位毛刺消除电路所能避免的毛刺长度,而延时器件的延时长度也决定需要提供有效复位信号的最短时间。

如果复位信号高有效,则将图3中的或门改为与门使用。为更好地消除毛刺,可在复位毛刺消除电路后再加上寄存器对复位信号进行时钟同步。在通常复位电路的设计中,毛刺的长度一般情况下>1个时钟周期,<16个时钟周期。为节省资源,延时器件通常选用SRL16。SRL16可设置初始值,但不带复位功能16bit移位寄存器,能够通过A0~A3的4根地在线选择从第几个寄存器输出。通常将其作为一个普通的16bit移位寄存器使用。

3.2 异步复位同步释放

在有些应用中,复位信号需要在时钟尚未给出或不稳定的情况下传到后级,在时钟稳定之后,再撤去复位信号。此时需使用异步复位来实现。由于异步复位时,时钟和复位关系的不确定性,易造成触发器输出亚稳态,引起逻辑错误。为确保其复位的可靠性,通常采用异步复位,同步释放的方式。

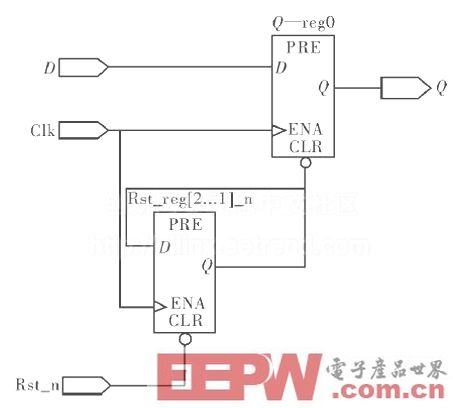

所谓异步复位,同步释放就是在复位信号到达时不受时钟信号的同步,而是在该信号释放时受时钟信号的同步。通过一个复位信号综合器便可实现异步复位,同步释放。综合后的RTL图如图3所示,其仿真结果表明该电路能有效的实现复位及脱离复位。

图3异步复位、同步释放电路图

3.3 采用专用全局异步复位/置位资源

全局异步复位/置位资源的主要作用是对系统中存在的所有触发器、锁存器、查找表单元的输出寄存器进行复位,不会占有额外的布线资源。使用GSR资源,异步复位到达所有寄存器的偏斜最小。

3.4 采用内部复位的设计方法

在无需复位信号先于时钟信号产生的应用中,为避免外部复位毛刺的影响、异步复位电路可能引起的亚稳态以及减少资源的使用率,可通过FPGA产生内部复位,然后采用异步的方式对其的内寄存器进行复位。由于该复位信号由FPGA内部产生,不会因外部干扰而产生毛刺,同时又与时钟同步,不存在因异步复位导致的亚稳态现象,因此可确保系统可靠复位。

4 结束语

FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。在工程实践中,上述方法可以有效减少或消除FPGA复位所产生的错误。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)