一种基于HD-SDI技术的高清图像处理系统设计

设计的数据发送单元由一个DVI编码器和一个PAL编码器组成。其中,DVI编码器将数字信号转换为差分信号,传递给DVI接口高清显示器。DVI接口需实现1080P高清显示,是数据发送单元的关键环节。

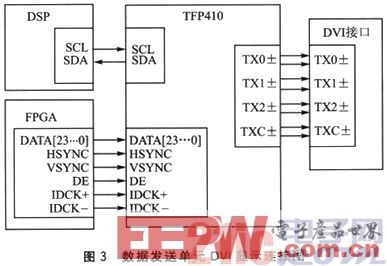

针对图像输出接口的不同要求,选择NXP公司的SAF7129实现图像的PAL制式输出;选择TI公司的TFP410实现DVI图像输出。其中,DVI显示为数字信号输出,与传统的VGA模拟信号相比,采用DVI数字信号不会引起像素抖动和相邻像素间的干扰,显示器不会造成几何失真,大大提高了画面质量,显示画面细膩、清晰,因此设计时将DVI接口作为系统的主显示通道。PAL制式为模拟信号输出,可以兼容光电系统在特殊情况下的显示需求。数据发送单元DVI显示连接如图3所示。

TFP410支持从VGA到UXGA(25~165 MHz)格式的像素速率,具有12位双边和24位单边两种输入模式,可以通过I2C总线进行芯片工作模式配置。TFP410主要通过DE引脚的高低电子来决定发送信号类型。当DE为高电平时,发送像素编码数据;当DE为低电平时,发送同步信号以及控制信号。

本设计通过I2C总线来配置编码器,编码器采用24位单边输入模式,单边输入时钟,下降沿触发。采用I2C总线可以快捷地在线调整参数配置,对编码器高速输入信号的时钟沿进行调整,有效减少图像噪声和串扰。

4 图像存储单元

图像处理系统输入一帧1080P高清图像的大小为:

1 920×1 080×16=33 177 600位=30 Mb

选择了CYPRESS公司CY7C1482V33型号的SRAM作为系统图像存储单元,CY7C1482V33存储空间大小为72 Mb,可配置为2M×36位,4M×18位,1M×72位,能同时存下2幅图像。CY7C1482V33支持最高达250 MHz的读写速度,工作电压为3.3 V。

5 FPGA处理单元

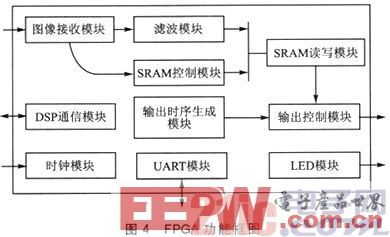

FPGA主要完成图像采集、存储、输出显示管理,与DSP之间进行数据交互以及视频的像素级处理,是图像处理系统的核心管理单元,与图像有关的功能框架模块大部分都在FPGA中实现。FPGA功能框图如图4所示。

当数据发送单元传递1920×1080像素图像格式的数据给FPGA后,根据每帧图像20位YCbCr 4:2:2工作模式的要求将亮度和色度信息分开提取。SRAM是单端口存储器,在同一时间只能完成读操作或写操作,因此在输入数据进行滤波后,选用了2M×36位的3片SRAM作为一组片外存储器进行Ping-Pong操作。用输入SDI图像的场同步信号生成一个计数器,每一场对SRAM的读写切换一次。当需要使用一场图像信息时,可及时从一个存储器中读取。与此同时,连续的图像数据被存至另一个存储器中,第3片SRAM则处于DSP读写状态。3片SRAM通过切换,完成一帧图像的保存、处理和输出。

6 软件设计

系统的软件主要包括FPGA和DSP两部分。FPGA负责采集和输出电视图像数据,利用FPGA内部的存储资源,进行字符、十字丝、波门等信息叠加,不仅提高了数据处理速率,而且降低了DSP处理数据时产生帧间延时的可能性。DSP负责通过SPI配置和检测HD-SDI解码器,实现视频模式选择,并根据检测结果确定各个芯片当前的工作状态,此外通过访问图像存储器进行Mean-shift、非对称多向梯度、质心、相关、电子稳像和航迹预测等算法运算。

上电之后,对DSP进行初始化,主要包括片外存储器、SPI、GPIO、外部中断的配置。初始化完成之后,通过SPI向GS2971发送开始解码的指令,向GS2971请求状态信息,等待GS2971进入到解码状态,更新FPGA的采集数据。

DSP从图像存储器得到图像数据后,根据背景的复杂程度和上位机命令执行图像质心、相关跟踪与航迹预测算法。经过DSP图像处理后,判断出锁定的运动目标,并计算出所跟踪目标的角坐标值和跟踪角误差值,传递给上位机进行实时控制。同时把跟踪目标的位置信息叠加到SRAM内相应的视频帧,经DVI通道将电视数据送到高清显示器上显示。

结语

HD-SDI既满足了传输高清图像的要求,又能最大限度保证传输过程的实时性,能够适应当今图像跟踪技术的发展。本文设计开发了基于HD-SDI的高清图像处理系统,与传统模拟图像相比大幅度提高了图像细节质量和跟踪稳定性,为光电系统提供了新的解决方案。可在光电系统的新发展中得到广泛应用,具有良好的应用前景。

- 彩色低照度HD-SDI高清摄像机的市场定位(01-08)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)