基于ARM核的音频解码器单芯片系统研究

的外部存储器系统上是可能的。ARM720T控制寄存器中的大端/小端位设置了EP7209在处理存储器中的字时是按大端格式还是小端格式进行。存储器被认为是从0开始向前编号的字节的线性组合。字节0~3容纳第1个被存储的字,字节4~7容纳第2个字,等等。在小端规划中,字中编号最低的字节认为是字的最低位字节,而编号最高的字节被认为是字的最高位字节。存储系统的Byte0在这个规划中应当连到数据线7到0(D[7:0])。在大端规划中,字的最高位字节被存储于编号最低的字节中,而最低字节存储于编号最高的字节中。因此,存储器系统的Byte0应当连到数据线31到 24(D[31:24])。装载和存储指令是被大小端配置影响的唯一指令。

9. 支持片上帧缓冲器的LCD控制器

LCD 控制器提供了所有需要的控制信号以便直接与一个单面板复合LCD接口。面板的大小是可编程的,可以是以16像素为增量,从32到1024像素的任何宽度(线长度)。总的视频帧缓冲大小可编程为高达128KB。这等同于理论上最大的面板大小1024×256像素(每像素4个位 )。视频帧缓冲器可定位于任何一个片选所控制的存储器中。在任何一个片选所控制的存储器中,它的起始地址固定于地址0X00000000。LCD视频帧缓冲器的起始地址定义在寄存器FBADDR[3:0]中,这些位将成为外部地址总线的最重要nibble(半字节)。缺省起始地址为 0XC0000000(FBADDR=0XC)。一个使用片上SRAM(OCSR)建立的系统将把片上SRAM用于LCD视频帧缓冲以及用于各种数据的存储。LCD视频帧缓冲器起始地址在这个系统中应当设置为0X6。

三、内存映射

地址空间的低2GB分配给了存储器。在EP7209中,恰好在2GB下的8KB的空间是为内部寄存器所准备的且不可存取,EP7209的MMU应被编程为在访问这一区域时产生一个中断例外。

通过从十六进制地址8000.0000到8000.3FFF的一组内部存储器位置来寻址内部外围部件。这些内存位置在EP7209中被认为是内部寄存器。从0x8000.0000到0x8000.1FFF含有与CL-PS7111兼容的寄存器,包含了这些寄存器是为了向下兼容并称它们为旧的内部寄存器。

表2显示了ARM720T处理器的4GB地址空间范围在EP7209中是如何被映射的(当从片上启动ROM启动时将有不同的内存映射),所显示的内存映射假定两个CL-PS6700卡控制器连结上了。如果此功能不需要的话,那么nCS[4]和nCS[5]存储器空间是可用的。外部启动ROM没有被完全解码(即:启动代码在0x7000.0000到0x8000.0000的256MB字节空间内将重复)。SRAM可被完全解码至最大的大小,即128KB,对超出此范围的任何位置的存取将绕回到这个范围内。

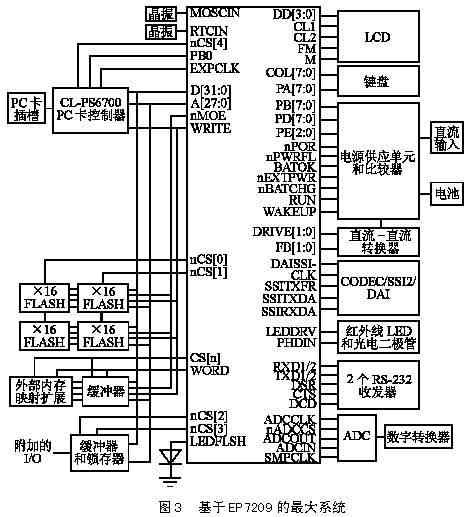

四、基于EP7209的最大系统

基于EP7209的最大配置系统如图3所示。此系统假定ROM为16位宽的器件。键盘可以连接到比图3所示更多的通用输入输出端口位,以支持多于64个键;然而,这些额外引脚将不能引线到WAKEUP引脚。

需要注意的是,三个串行接口(DAI、CODEC和SSI2)的输入/输出是多路复用同一组外部接口引脚的。因此,在任一时刻,系统只能使用这三个外围器件接口中的一个。

结束语

本文介绍了一种基于ARM核的音频解码器单芯片系统EP7209。描述了EP7209的整体结构、各功能块以及ARM处理器的地址空间在EP7209中是如何映射的。对EP7209的基本工作原理进行了讲解。最后给出了基于EP7209所能够构建的最大系统。希望本文能够使嵌入式系统的开发人员了解 EP7209并加深对ARM核的理解。

参考文献

1 EP7209 Datasheet.Cirrus Logic, Dec., 1999

2 Jaggar Dave. ARM Architecture Reference Manual. Prentice Hall, 1996(7)

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)