基于ARM核的音频解码器单芯片系统研究

摘 要: 简要介绍Cirrus Logic公司的嵌入式处理器产品EP7209的结构、功能、接口特性等,并给出基于EP7209所能构建的最大系统。对使用EP7209构建嵌入式系统有一定参考价值,也有助于了解ARM核。

关键词:嵌入式处理器 嵌入式系统 ARM核

引 言

EP7209是世界上第一片既支持流行的MP3标准,也支持诸如Microsoft Audio等快速涌现的互联网音频压缩标准的数字音频解码器片上系统。EP7209在74MHz下运行时其性能与基于100MHz英特尔奔腾芯片的个人计算机相同,且消耗的功率特别小:在2.5V电压下,功耗不足170mW。它的ARM核提供了一个优秀的数字信号处理器所能够提供的处理能力,因此,互联网音频处理仅占用了该芯片50%的处理能力。这给嵌入式系统的设计人员留下了高达25MIPS(百万条指令每秒)的处理能力用于实现其它功能。本文着重讨论 EP7209的结构、功能、接口特性等及其在嵌入式系统中的应用。

一、功能框图及功能块描述

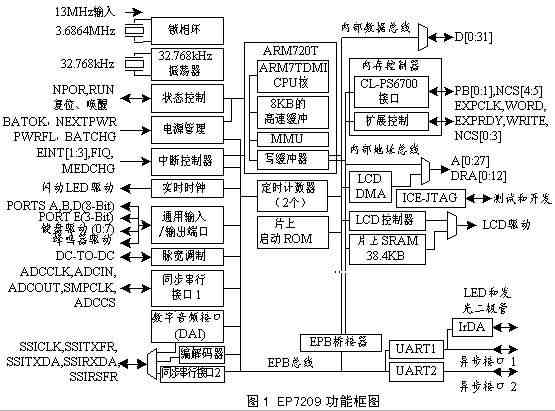

图1是EP7209的功能框图。由图1可知EP7209含有如下功能块。

(1)ARM720T处理器含有如下功能子块:

① ARM7TDMI CPU核。该CPU核支持Thumb指令集、核调试、增强的乘法器、JTAG以及嵌入式ICE。它的时钟速率可编程为18MHz、36MHz、49MHz、74MHz。

② 内存管理单元(MMU)与ARM710核兼容,并增加了对Windows CE的支持。该内存管理单元提供了地址转换和一个有64个项的转换旁路缓冲器。

③ 提供了8KB的单一的指令和数据高速缓冲存储器以及一个四路相联高速缓冲存储器控制器。

④ 写缓冲器。

(2)38400字节的片上SRAM,可以在LCD控制器和通用应用之间共享。

(3)内存可以和高达6个独立的扩展段接口,每个扩展段有256MB,且等待状态可编程。

(4)27位的通用I/O,可以多路复用,以在需要时提供额外的功能。

(5)数字音频接口(DAI)可以直接与CD音质的DAC和编解码器相连。

(6)中断控制器。

(7)先进的系统状态控制及电源管理。

(8)2个16550A兼容的全双工UART,含16字节的发送及接收FIFO。

(9)SIR协议红外线数据编解码器,速率最高达115.2kbps。

(10)LCD控制器,16级灰度,可编程为1、2或4位每像素。

(11)片上的启动ROM,已固化了用于串行加载的启动代码。

(12)2个16位的通用定时计数器。

(13)1个32位的实时时钟(RTC)和比较器。

(14)2个同步串行接口,用于诸如ADC等Microwire或SPI外围器件。一个接口支持主模式和从模式,另一个仅支持主模式。

(15)完全的JTAG边界扫描和嵌入式ICE支持。

(16)2个可编程的脉冲宽度调制接口。

(17)1个用于和1或2个Cirrus Logic CL-PS6700 PC卡控制器器件相连的接口,可支持2个PC卡插槽。

(18)振荡器和锁相环,用于由外部的3.6864 MHz的晶振产生内核所需要的18.432MHz、36.864 MHz、 49.152MHz或73.728MHz的时钟。此外还有一个外部时钟输入端(在13MHz模式下使用)。

(19)一个低功耗的32.768kHz的振荡器,用于产生实时时钟所需要的1Hz时钟。

所有的外部存储器和外围器件都应连接到32位的数据总线D[0:31]上,并应使用28位的地址总线A[0:27]和其它控制信号。

二、基本工作原理

EP7209的核心逻辑功能是建立在一个ARM720T嵌入式处理器之上的。对EP7209的设计,以低功耗为目的进行了优化,并使用完全静态的 0.25μm的CMOS制造工艺。低功耗的思想同样体现在状态设计、时钟使用的方式上。下面将有选择地介绍EP7209的工作原理。

1.CPU内核

ARM720T由一个ARM7TDMI 32位RISC处理器、一个单一的高速缓冲和一个存储器管理单元(MMU)所构成。8KB的高速缓冲有一个四个项的相联寄存器,并被组织成512线四字 (4×512×4字节)。高速缓冲直接与ATM7TDMI相连,因而高速缓冲来自CPU的虚拟地址。当所需的虚拟地址不在高速缓冲中时,由MMU将虚拟地址转换为物理地址。一个64个项的转换旁路缓冲器(TLB)被用来加速地址转换过程,并减少页表读取所需的总线传送。仅通过转换高速缓冲中未存储的地址,MMU就能够节约功率。

2.状态控制

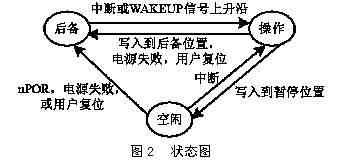

EP7209支持如下的电源管理状态:操作、空闲和后备(节能),如图 2所示。正常的程序执行状态为操作状态。这是一个完全性能状态,时钟和外围器件都被使能。除了CPU时钟被暂停外,空闲状态与操作状态是一样的。一个中断或唤醒将使空闲状态返回到操作状态。后备状态下功耗最小,选择此模式会关闭主振荡器,只对实时时钟和相关逻辑提供电源。当EP7209处于后备状态时,为保证系统能够正常唤醒,所有电源和地引脚仍然与电源和地相连是非常重要的。后备状态唯一能够变迁到的状态是操作状态。

3.复 位

EP7209有三个异步复位信号:nPOR、nPWRFL和nURESET。如它们中的任一个有效,

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)