下一代FPGA有望实现突破性优势

其他工艺技术能够完善Intel的14 nm三栅极工艺,例如,TSMC的20SoC和55 EmbFlash,以实现多种系统设计目标。

例如,TSMC的20SoC工艺支持客户在产品中采用下一代FPGA,在能够使用14 nm器件之前,就可以投入到大批量宽带基础设施市场中。客户的内核性能得到了提高,与目前大批量应用的功能相似的FPGA相比,系统可以运行在500 MHz以上,其ARM?处理器高达1.5 GHz,而功耗降低了50%。这一20 nm工艺是客户满足关键目标的基础,例如,电信、数据中心和其他应用所要求的单位比特成本和每瓦性能。嵌入式闪存工艺等其他工艺支持系统设计人员获得单位I/O引脚最低成本,支持低功耗解决方案,还可以采用模拟电路和非易失闪存,而这是其他工艺在经济上无法实现的。

体系结构和IP

为满足比当今应用高出四倍的带宽性能需求,应采用更先进的工艺技术。这需要新的逻辑体系结构、新IP,以及新的串行连接等。

下一代体系结构与前沿工艺技术相结合,能够显著提高内核性能。例如,Altera最近发布了新的高性能体系结构。与Intel的14 nm三栅极工艺结合后,其内核速率达到了令人吃惊的1 GHz。

这一体系结构极大的提高了数字信号处理(DSP)能力。这些DSP模块已经应用于FPGA中,而浮点运算的效率会更高。FPGA支持其性能达到每秒10兆次浮点运算(teraFLOPS)。将提供每瓦每秒100 giga浮点运算(GFLOPS),是性能最好、功效最高的解决方案之一,这对于现有DSP或者图形处理单元(GPU)是无法想象的。这将在金融、能源、云数据分析等高性能、大数据量计算应用中实现突破性功能。

通过提高数据速率、通道数量,包括更多的硬核特性,也将大幅度提高串行带宽。FPGA公司宣布其下一代收发器技术数据速率将达到56 Gbps。Altera等公司目前提供的单管芯FPGA的收发器数据速率是28 Gbps。单单下一代FPGA的28 Gbps通道数量就将增加四倍,实现下一代100G光接口的多个例化,例如CFP2、CFP4和QSFP28等。采用自适应判决反馈均衡器(DFE)等增强信号调理技术,即使是在电噪声环境中,收发器也满足了高损耗背板应用需求。而且,使用增强前向纠错(FEC)等技术,能够克服30 dB通道损耗,延长背板传输距离,支持使用低成本材料,而不会牺牲系统误码率(BER)。功能的增强提高了收发器的可用性。例如,硬核物理编码子层(PCS)模块可以处理8b/10b和64/66b等多种编码方法,还为Interlaken和10 Gbps以太网(GbE)数据流提供关键的处理功能。而且,为PCI Express? (PCIe?) Gen1、Gen2和Gen3提供全面的协议栈。今后的FPGA将大规模采用串行存储器。串行存储器接口采用了10-15 Gbps高速串行收发器,克服并行存储器接口的带宽、延时和功耗局限。请参见图4。

图4.28 Gbps工作,采用了Altera的20 nm工艺技术

虽然某些应用需要最新的体系结构、IP和串行技术,例如,400G解决方案,但是,这对于其他应用不一定是最优方案,反而有可能影响其功耗和成本目标。有必要针对不同的FPGA和不同的应用而有选择的使用这些技术。

处理器集成

FPGA总是能够提高电路板上组件的集成度,而影响最大的是最近集成了基于ARM的硬核处理器系统(HPS)。HPS集成了独立但是高度集成的处理器以及硬核外设和可编程逻辑,开发了芯片系统(SoC)解决方案。这种集成是从28 nm可编程逻辑技术和ARM Cortex?-A9处理器开始的,FPGA中的这种体系结构得到了广泛应用,这些SoC的发展将为ARM处理器供应商的长期产品发展路线产生积极影响。系统规划人员现在有更多的选择来提高集成度,增强系统性能、降低系统成本和功耗,减轻供应链风险。没有采用这些可编程SoC的系统规划人员会吃惊的发现:

■ 不同类型的器件系列有大量的SoC产品

■ 可编程逻辑和处理器之间的紧密集成提高了性能,降低了延时。

■ 工程师通过28 nm SoC、开发套件和工具来使用这一新技术

■ 部分FPGA供应商提供ARM辅助系统支持

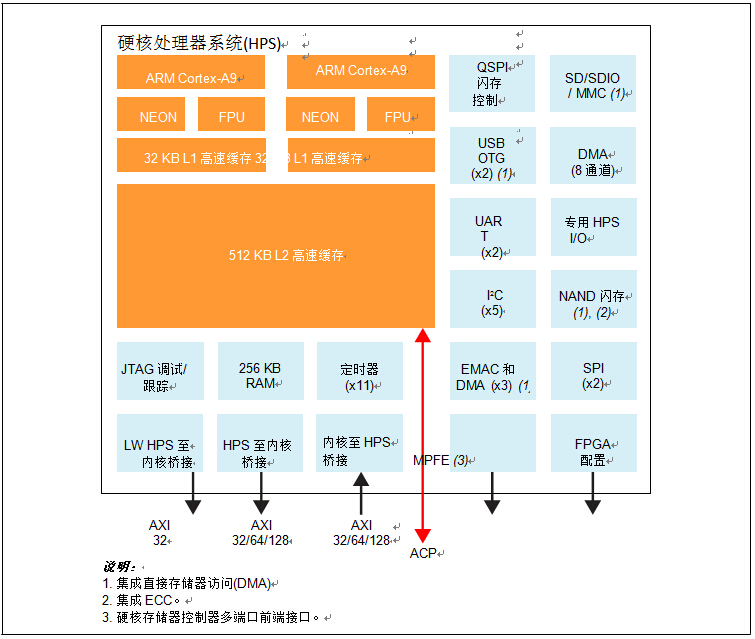

图5显示采用了ARM Cortex-A9处理器的第二代HPS模块。

图5.采用了ARM Cortex-A9处理器的第二代HPS模块

下一代FPGA和SoC即将出现

28 nm工艺节点之后发布下一代PLD的第一家公司是Altera,推出了10代系列产品。Altera使用了定制方法,所有PLD提供商在其各种低成本、中端和高端产品系列中广泛使用了不同的工艺技术、不同的体系结构和IP以及不同的集成方法。第10代系列产品包括Stratix? 10以及Arria? 10 FPGA和SoC,满足了需要一些中等速率收发器的应用需求,以及需要多

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)