基于FPGA的模糊控制器管理蔗糖提取

在实现以上步骤后,我们成功使用三角从属函数和中心去模糊法设计出一种三输入模糊控制器。程序代码已经由作者提供。我们使用 MATLAB 7.11.0.584 版本 (R2020b) 的 Fuzzy Toolbox 仿真三输入模糊控制器,并利用赛灵思的 ISE® Design Suite14.5 并使用 VHDL 在赛灵思 Virtex-6 FPGA上 将其实现。采样周期为10 秒,仿真总时长为 200 秒。

我们调差了六个不同情况下总共 756 种不同的输入参数条件,但我们重点研究的是仿真最初阶段传送带上甘蔗高度和甘蔗重量分别为 90cm 和 750kg 的这种情况。辊速在每次抽样时均有所变化。表 1 给出了仿真结果。

表 1–甘蔗高度在 90cm 时,每次抽样辊速都不同。

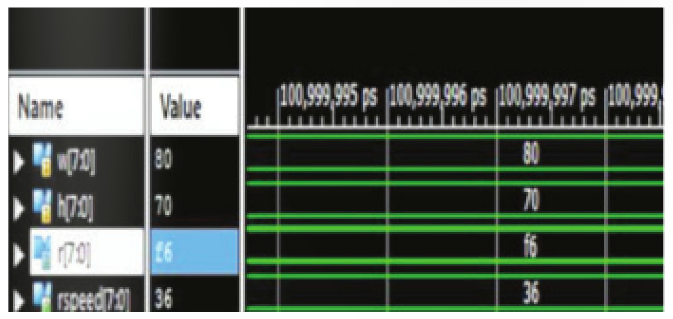

图 4:当重量为 750kg,高度为 90cm,辊速为 16.6 cm/s 时的仿真波形

硬件实现步骤包括在我们 MITS 校园实验室中进行的 VHDL 建模、仿真、综合和 FPGA 实现。我们使用混合型建模方法来设计三输入模糊控制器的 VHDL 模型,其中包括行为建模和结构建模。该设计在赛灵思的 ISim 仿真器上进行仿真。ISim 生成的波形用来验证控制器的功能。图4 给出了倾斜传送带中甘蔗重量为 750kg,Donnelly 榨糖机中甘蔗高度为 90cm,辊速为 16.6cm/s 时的仿真波形。在这些条件下,期望的倾斜电机速度为 54.2rpm (MATLAB)。去模糊化仿真结果为 36H 或 54 rpm,与 MATLAB 结果匹配,并验证了设计。

仿真之后,我们对设计进行综合,以生成技术原理图和粗略的器件利用报告。我们发现我们的设计使用了 78% 以上的 Virtex-6 Slice 查找表 (LUT),93% 的已占用 Slice,1% 的 Slice 寄存器,以及 1% 的 LUT 触发器。

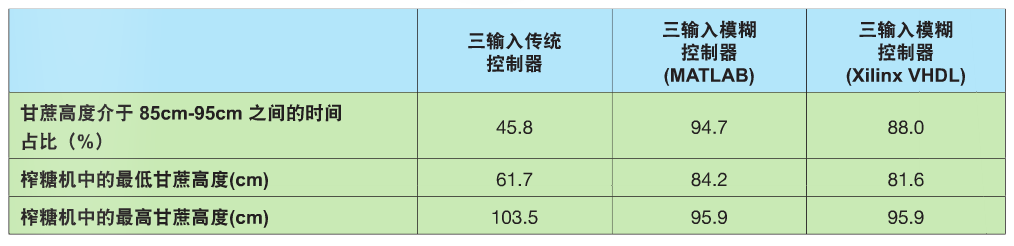

然后,我们将 VHDL 结果与传统控制器结果进行对比(见表 2)。对比结果表明模糊逻辑系统比传统控制器效率更高。位于 MITS 的实验室提供一块用于研究的 Spartan®-6 FPGA。然而,我们发现所需的 LUT 模块数量超出了目标器件的容量。这就是为什么我们转而在 Virtex-6 上实现设计。但是,由于缺少资源,我们无法在实验室中进行实时实现。下一步中,我们希望与印度国家制糖学会管理部门联合开发整个系统,并在真实环境中验证结果。我们已经向印度国家制糖学会交付方案演示,并收到了正面回应。我们坚信模糊逻辑概念很有可能改变制糖工业的未来。

表 2–结果对比

参考资料

1. Y. Misra 与 H.R.Kamath 共同编撰的“为保持制糖过程中甘蔗的水平高度专门设计一种传统模糊控制器算法”,摘自《智能系统与应用国际期刊》,期刊编号:2074-9058,第 7 卷第 1 章,2014 年 12 月

2. Y. Misra 与 H.R.Kamath 共同编撰的“《在使用 VHDL 的 FPGA 中对三输入传统控制器进行实现方案与性能分析,以确保甘蔗压榨过程中甘蔗水平高度”, 摘自《工程研究与技术国际期刊》(IJERT),期刊编号:2278-0181,第 3 卷第 9 期,2014 年 9 月

3. Y. Misra 与 H.R.Kamath 共同编撰的“对用于保持制糖过程中甘蔗高度的三输入模糊系统进行分析和设计”, 摘自《自动化控制杂志》(已接受),期刊编号:2372-3041

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)