三大电机控制方案之FPGA篇:Actel Fusion

当前电机控制的发展越来越趋于多样化、复杂化,现场也提出越来越苛刻的性能要求。因此客户有可能考虑自己开发专用的控制芯片,FPGA的可编程性正是可以满足这种需求。上期讲解了三大电机控制方案之MCU篇,这期来看看FPGA。

对于电机控制提出的不同要求,FPGA芯片固有的可编程性和并行处理的特点十分适合于中高端的电机控制应用。由于它以纯硬件的方式进行并行处理,而且不占用CPU的资源,所以可以使系统达到很高的性能。

在电机控制的市场上,众多专注于FPGA技术的厂商接连推出了各具特色的解决方案,本系列将会为大家介绍这些厂商以及它们在电机控制领域的代表产品。首先,是身为FPGA三大巨头之一的Actel 公司。

Actel Fusion系列器件

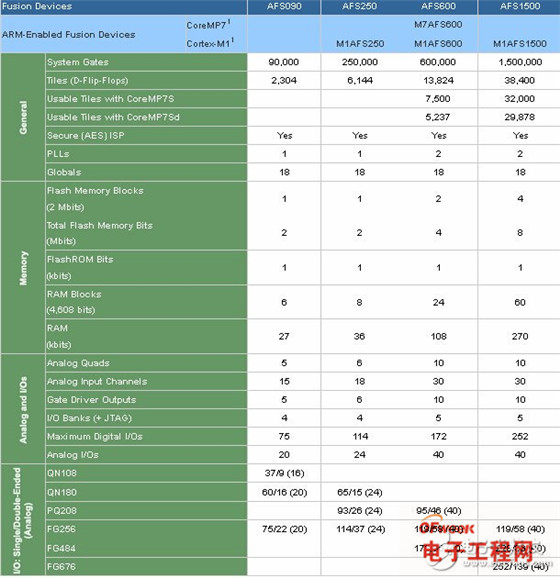

Actel Fusion系列器件是业界首款也是唯一具有模拟功能的Flash架构的FPGA,融合了FPGA数字内核、A/D转换器、Flash存储器、模拟的I /0、RTC等数字和模拟器件。Fusion器件内部具有2~8 Mbit不等的用户可用Flash存储器和30通道、最高12位精度、最高600 Ks/s采样率的A/D转换器,片内100 MHz的RC振荡器与PLL(锁相环)一起共同为FPGA提供时钟,以节省外部时钟的开销。这些特点极大地提高了该系列FPGA器件的功能,简化了系统设计,大幅度减少了电路板面积和系统总成本。当Fusion系列FPGA器件结合8051,CortexMl,ARM7等软件MCU核时,还可以实现真正的 SoC系统。Actel Fusion系列器件的众多特点,使其在电机控制的领域得到了广泛的应用,由它延伸出来的Smartfusion 数模混合芯片,十分适合高复杂度电机控制的应用。

产品一览

Actel Fusion的特点

单芯片

以 Flash 为基础的 FPGA 将配置信息储存在片上 Flash 单元中,一旦完成编程后,配置数据就会成为 FPGA 结构的固有部分,在系统上电时并无需载入外部配置数据。以 Flash 为基础的 Fusion 融合 FPGA 无需额外的系统元件,如传统 SRAM FPGA 配置用的串行非挥发性内存 (EEPROM) 或以 Flash 为基础的微控制器,它们都是用来在每次上电时对传统 SRAM FPGA 加载程序的。增加的融合功能可在电路板上省去多个附加元件,如 Flash 内存、分立模拟 IC 、时钟源、EEPROM ,以及实时时钟等,从而减低系统成本和电路板空间需求。

低功率

Fusion 器件具有类似于 ASIC 的功率特性,因而适用于电池供电产品和其它对功耗敏感的应用。使用Fusion 器件时,并不会出现加电浪涌电流和大电流转换,而这是许多 SRAM FPGA 器件所面对的问题。Fusion 器件还具有低静态和动态功耗,能实现最多的功率节省。这些器件支持睡眠和待机模式运作,可大幅降低功耗。Fusion 器件的另一个独特性能是在非活动期间于正常时钟速度和低时钟运作速度之间进行动态转换,并在需要时转为全速运作。

上电即行

以 Flash 为基础的Fusion 器件具有上电即行 (LAPU) 特性,一旦施加正常运作规格内的系统功率,Fusion 器件即可工作。这种上电即行特性能够大幅简化整体系统设计,并往往可以省去系统中复杂的可编程逻辑器件 (CPLD) 。

安全性

Fusion 器件包含了 Microsemi FlashLock? 功能,提供可重编程性和设计安全性的独特组合,且无外部元件费用。这些优点只有通过带非挥发性 Flash 内存的 FPGA 才能实现。Fusion 器件具有基于 Flash 的 128 位安全保护机制和业界领先的片上 AES 解码内核,用于保护经编程的 IP 和配置数据。 128 位 AES 是政府机构认可速度更快、安全性更高的加密算法,可以替代 DES 。目前,Fusion 器件具有最完备的可编程逻辑安全解决方案。以 AES 加密技术为基础的Fusion 器件可让设计人员安全地完成系统设计和 Flash 内容的远程更新 (通过公共网络如互联网等),确保具价值的 IP 不会遭受系统过建、复制和 IP 盗窃等问题所侵害。虽然编写在Fusion 器件中的 FPGA 设计不能读回,但可对其进行安全的设计验证操作。Fusion 器件采用了许多器件设计和布局工艺技术,使到入侵攻击难以得逞。例如,Fusion 器件的 Flash 单元都位于 7 层金属层之下,因而极难实现反向工程。

固件错误

固件错误是高层大气中产生的高能中子撞击 SRAM FPGA 配置数据存储单元所导致的错误。撞击产生的能量会改变 SRAM FPGA 配置数据存储单元的状态,从而改变其逻辑、路由或 I/O ,而这种改变是无法预测和控制的。这类错误在 SRAM FPGA 中不可能避免,因而导致其时间延续故障 (FIT) 率值达数千。这类错误可能导致整个系统失效,引起重大的技术支持和产品可靠性问题。融合 FPGA 的配置元素 (即 Flash 存储单元) 便不会被高能中子改

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)