PCI总线接口设计及专用接口芯片的应用

1 引言

随着计算机技术的飞速发展和普及,数据采集系统迅速得到了广泛的应用。数据采集系统性能的好坏主要取决于它的精度和速度。在保证精度的条件下,应用尽可能高的采样速度,以满足对信号的实时采集和实时处理;而要实现高速数据采集,不仅需要高性能的adc等设备,而且需要高速的数据传输。目前isa总线己经逐 渐退出了历史舞台,开发基于pci总线的数据采集卡己经是势在必行。

2 pci总线接口概述

pci总线的信号线包括32根地址数据复用线、仲裁、接口控制线、总线命令字节允许复用线和系统复位等。在进行基本的数据传输操作时,数据线先出现地址, 同时总线命令出现在c/be〔3:0〕上,设备根据这些命令判断所要进行的操作,在接下来的数据节拍中传输数据,如果传送或接收方没有准备好,那么就插入等待周期。pci总线的其它操作还有设备选择、配置周期和中断应答等。

pci总线协议复杂,需要在外部设备和pci总线之间增加一个接口电路。接口电路实现比较困难,目前实现pci接口的方法主要有:利用cpld或fpga 可编程逻辑器件和利用专门的pci接口芯片等多种方法实现。pci接口芯片具有设计简单、功能强大、可靠性好等特点,从而大大减少了开发人员的工作量。在 实际工作中我们综合各方面的因素,在本文选择了pci9054。

3 pci9054芯片

3.1 pci总线通用接口芯片简介

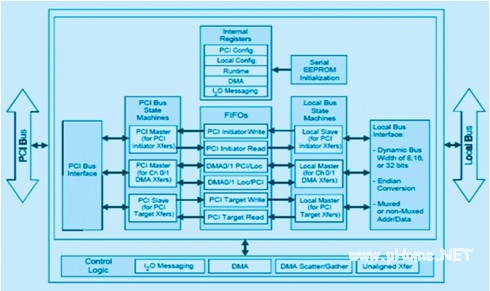

pci9054是plx公司生产的pci总线通用接口芯片,采用先进的plx数据管道结构技术,符合pciv2.1和v2.2规范;提供了两个独立的可编 程dma控制器;每个通道均支持块和分散/集中的dma方式;在pci总线端支持32位/33mh;本地端(local bus)可以编程实现8,16,32位的数据宽度;传输速率最高可达132mb/s;本地总线端时钟最高可达50mhz支持复用/非复用的32位地址数 据。pci9054的内部结构框图如图1所示。

图1 pci9054内部结构框图

由图1可知,pci9054提供了pci、eeprom、local总线三个接口。pci9054作为一种桥接芯片在pci总线和local总线之间提供 传递消息,既可以作为两个总线的主控设备去控制总线,也可以作为两个总线的目标设备去响应总线。

pci9054有6个零等待可编程fifo存储器(fifos)。它们分别完成pci发起读、写操作,pci目标读、写操作和dma读、写操作。由于 fifo存储器的存在,数据可以大量突发传输而不丢失。这样不仅满足实时性要求,同时可以根据用户的需要采用与pci时钟异步的本地频率。串形 eeprom(serial eeprom)是用来在开机时初始化配置内部寄存器的。内部寄存器(internal regi- sters)标识地址映射关系以及pci端和本地端工作状态。fifo和内部寄存器在计算机主机或者本地端都是统一编址的,用户可以从两端通过编程访问它 们的每一个字节。

3.2 数据传输模式

pci9054的数据传输模式灵活多样,包括直接主模式(pci master)、直接从模式(pci target)、dma模式。

数据传输模式的选择主要是要根据硬件设计者对硬件设计的需求而定的。当硬件设计者选择由pci发起控制的时候,则pci9054应该为pci的工作目标, 这时应选择pci 9054的工作方式为pci从模式。当硬件设计者选择本地端发起控制的时候,pci9054成为主控设备,而pci则成为pci9054的工作目标,这种 情况下应选择pci9054的工作方式为pci主模式。在数据进行dma传输时,pci9054对pci端和local端都是主控设备,本身具有dma控 制器完全可以脱离pc机进行dma控制,此时pci9054工作在dma传输模式。

3.3 本地总线工作方式

pci9054本地总线可工作在m,c,j三种模式。

m模式是专为motorola公司的mcu设计的工作模式。c模式下9054芯片通过片内逻辑控制将pci的地址线和数据线分开,很方便地为本地工作时序 提供各种工作方式,一般较广泛应用于系统设计中。j模式是一种没有local master的工作模式,它的好处是地址数据线没有分开,严格仿效pci总线的时序。pci9054的工作方式可利用模式选择引脚加以选择,对于 176pin-pqfp封装的9054芯片模式选择引脚为pin156(mode1)和pin 157(modeo)。只要将这两个脚接地便可选择了c模式;两个脚都接 则选择了m模式;pin156接地,pin157接则选择了j模式。

4 利用pci9054进行pci接口电路的设计

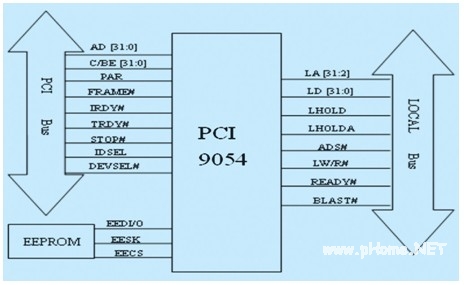

4.1 接口电路的硬件结构图如图2所示:

图2 硬件结构图

4.2 pci9054与pci bus接口

硬件接口电路的第一部分是9054与pci插槽间的连接信号线。这些信号包括地址数据复用信号ad[31:0],总线命令信号 c/be[3:0]和pci 协议控制信号par,frame#,irdy#,trdy#,stop#,idsel,devsel#等。电路连接中将彼此对应的信号线连接在一起即可。在pci总线信号中,除了rst#,inta#~in

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于DSP的PCI驱动程序开发 (04-08)