某型机载作战任务加载器的设计与实现

待状态和选通时序使得 DSP芯片可以和许多外部存储器或扩展外设间实现无缝接口。每个XINTF空间都有自己的时序寄存器XTIMING,改变时序寄存器的值将会影响相应空间的访问时序。1553B接口、RAM、数据存储卡可分别映射到不同的存储空间,实现简化设计。

2.2 1553B总线接口电路

作战任务加载器与火控计算机之间的数据传输通过1553B总线接口实现。本设计选择1553B接口芯片HK1553B来实现通信功能。

1553B总线接口电路工作时钟为12MHz,经过隔离变压器连接到1553B总线,模块上1553B芯片工作在RT方式下,1553B协议芯片访问外部存储器为一片64k×16bitSRAM存储器,存储器的访问控制及1553B协议芯片请求DSP总线及应答信号由FPGA产生。1553B协议芯片的地址和数据总线全部引入FPGA,1553B协议芯片访问DSP总线时地址数据通过FPGA挂在EMIF总线上。

2.3 USB接口电路

本系统采用的存储卡为MagicRAM公司的USBFlash存储卡,该存储卡读取周期最大为200ns,可执行100000次写/擦除操作。该存储卡的读写访问时序是典型的异步并行接口访问时序。DSP提供了对异步存储器的无缝访问接口XINTF,将数据存储卡单独映射到DSP的 Zone2外部存储空间。

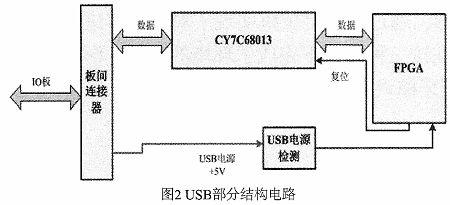

USB芯片CY7C68013与FPGA相连,在检测到USB供电后,通过FPGA实现对USB接口芯片的复位,并使能USB接口信号,实现与上位机的通信,完成调试加载功能。USB接口部分结构如图2所示。

FPGA通过USB口电源监控电路实现对USB接口的接口控制,当USB接口供电有效时,FPGA输出USB芯片复位有效,并使能与USB接口的数据总线,在USB不使用条件下USB工作在PowerDown模式,数据总线置为三态。

3 软件设计

作战任务加载器的软件分为三部分,包括驱动程序、BIT程序和应用程序,驱动程序由BIT程序和应用程序调用。驱动程序包括DSP初始化、1553B接口驱动、串口驱动、GPIO驱动等。DSP初始化对DSP的工作频率、XINTF总线时序、中断使能和优先级进行配置。1553B、串口接口驱动实现通信初始化配置、数据发送、数据接收等基本底层控制操作。

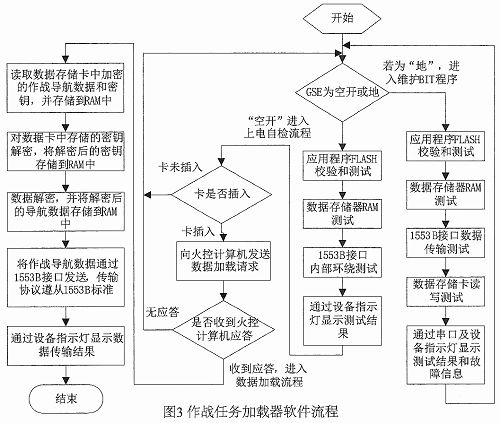

作战任务加载器BIT程序包括上电BIT和维护BIT。作战任务加载器上电后通过读取地面状态使能信号GSE#的状态进入地面工作模式或机上工作模式。

在地面工作模式,作战任务加载器执行维护BIT程序,对FLASH、RAM、1553B接口、USB数据存储卡等硬件资源进行测试,对FLASH的测试只进行应用程序校验和测试,对RAM、USB数据存储卡进行读写正确性测试,对1553B接口进行数据传输正确性测试。在机上工作模式,为了保证作战任务加载器的功能完备性,首先进行上电BIT测试,对应用程序FLASH校验和、数据RAM读写正确性、1553B接口内部环测正确性进行测试。上电BIT测试正确后,通过定时器产生定时中断不断侦测USB接口是否有数据传输卡存在。当正常插入数据存储卡后,任务加载器可向空地火控计算机发送数据加载请求,根据火控计算机的应答情况发起数据加载流程,执行应用程序。如未检测到数据存储卡或火控计算机无应答,则循环执行上电BIT测试。作战任务加载器的软件工作流程如图3所示。

应用程序对USB存储卡内密文数据和密钥读取,采用IDEA解密算法对密文数据解密,将解密后的明文数据通过1553B接口传输给空地火控计算机,其加载端和目标机均需支持1553B基本数据通信,通过握手-响应-确认机制来完成数据在加载端和目标机的可靠传输过程。

4 结束语

本文介绍了一种可读取USB数据存储卡并实现作战任务数据可靠传输的数据加载器。此设计方法可应用于更多具有安全可靠要求的数据加载设备。数据信息载体不局限于USB线性FLASH存储卡,可根据处理速度和数据量要求采用加固U盘、加固SATA电子盘等移动存储设备。与上位机的数据传输交互接口也可根据实际应用需求进行设计,可设计为AFD X、ARINC429、ARINC825等串行通信接口。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)