混合同余法产生随机噪声的FPGA实现

摘要:随着电子对抗技术的快速发展,在有源式干扰机中需要用到数字高斯白噪声。通过对混合同余法产生随机序列的原理研究,本文提出了一种利用FPGA产生高斯白噪声的方法。该方法在PC主控端的控制下,采用ROM查找表的方式实现信号的产生。在混合同余法的原理基础上,设计利用 MATLAB和QuartusⅡ软件对设计的高斯白噪声发生器进行仿真验证。应用Verilog HDL语言实现模块功能性,本设计采用Altera公司的StratixⅣ芯片EP4SGX230KF40C4ES。实验结果显示,本设计得到了稳定输出的数字高斯白噪声信号。

关键词:高斯白噪声;混合同余法;FPGA;Verilog HDL

电子战是战场敌对双方保护电磁谱为己所用同时防止被敌所用的科学艺术。电子战包括电子支持措施(ESM)、电子对抗措施(ECM)、电子反对抗措施 (ECCM)。电子干扰是电子对抗的重要组成部分之一,而有源压制式干扰是电子干扰中的一种常用手段。有源压制式干扰一般采用噪声调制,目的是尽可能大地降低被干扰雷达接收机中的信噪比,从而降低雷达的发现概率。在压制式噪声干扰中,噪声干扰都是采用随机噪声信号对VCO进行调制的干扰。因此在电子对抗领域里,噪声始终是最基本、最常用的干扰源之一。如何产生稳定和精确的噪声信号已经成为一个重要的研究领域。

随着FPGA技术的高速发展,数字噪声发生器的性能也得到了快速的发展。相对于传统的物理噪声发生器,基于FPGA的硬件电路噪声发生器具有实现简单方便灵活,易于扩展的优势。文献提出了一种基于M序列的高斯白噪声产生方法,该设计选取3个线性反馈移位寄存电路(LFSR),每个时钟生成一个32bit的均匀分布的随机数,序列具有的周期大约为288,足以满足实际工程需要。但是在该设计中1片FPGA内集成了均匀分布白噪声模块,FIR数字低通滤波器,均值和方差控制电路,耗费FPGA资源较多,结构较为复杂。

文献介绍了混合同余法和中心极限定理,论证了在此方法上可以产生服从正态分布统计特性的随机数。本文在此基础上,提出了一种基于混合同余法的FPGA随机噪声发生电路设计。设计通过主控端控制FPGA从直接波形ROM中读取数据,节省了FPGA片内的加法器和乘法器资源,结构简单,可靠性高。

1 混合同余法原理介绍

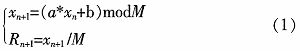

通过同余运算生成伪随机数的方法称为同余法,常用的同余法包括加同余法、乘同余法、混合同余法、除同余法。其中乘同余法和混合同余法的性能更好,有速度快、内存省、周期长、统计特性好等优点。混合同余法是Lehmer在1951年提出的,混合同余法是加同余法和乘同余法的混合形式,其迭代式如下:

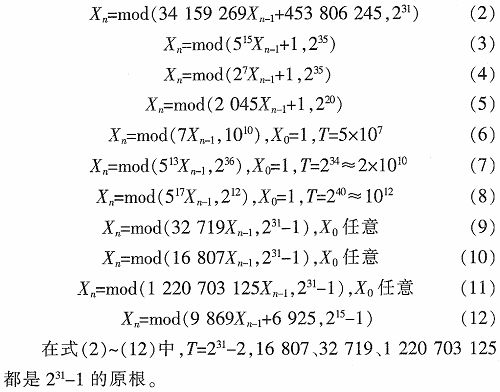

式(1)中a为乘子,xo为种子,b为常数,M为模。混合同余法是一种递归算法,即先提供一个种子x0,逐次递归即得到一个不超过模M的整数数列。集合 {xn}是由0到M-1的全部整数重新排列而成。当b=0时,称此算法为乘同余法;若b≠0,则称算法为混合同余法。xn是在(0,M)内服从均匀分布的随机变量,Rn则是在(0,1)内服从均匀分布的随机变量。式中x0,a,b,M的取值并不是随意的,模M大小是发生器周期长短的主要标志,常见的M为素数,取b为M的原根,则周期T=M-1。试验统计表明,用以下参数进行混合同余法产生的随机序列的统计特性较好:

混合同余法产生的随机序列具有以下特点:

1)xn重复周期较小,由于xn取值在(0,M)内,其周期,T≤M,T受x0,a,b,M值的影响。另外,在编程时,浮点运算也会对T产生影响。

2)用此方法产生的随机序列,在一个周期内任意两个随机数不可能相等,这往往与实际情况不相符。

经Hull和Dobell证明,只有x0,a,b,M满足以下一些关系才能实现周期最大化,即T=M,条件如下:

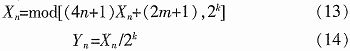

1)b与M互质(或互素,即它们的最大公约数为1)2)设q为某一质数,M分别能被q和4整除,且a-1能被q和4整除产生具有最大周期的伪随机序列的混合同余法算法为:

由于M=2k,k≥2时,M只有一个素数因子2,且4也是M的因子,此时a=4n+1,正好满足了T=M的第二个条件;而此时b=2m+1,刚好与M互质,即满足T=M的第一个条件。

可以看出,混合同余法产生的随机序列最多只能有M个不同的取值。为了获得长周期的随机数序列,应尽可能取大的M值,并合理选择其它参数。

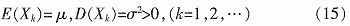

利用混合同余法产生的是在(a,b)区间上均匀分布的随机序列,再根据中心极限定理,就可以得到服从正态分布的随机序列。由独立同分布中心极限定理有:设随机变量X1,X2…Xn相互独立,服从同一分布,且具有数学期望和方差:

2 方案设计

本文设计的高斯白噪声发生器的系统结构框图如图1所示,首先在PC控制端根据式(17),应用MATLAB产生需要的高斯白噪声数据并存入RO

高斯白噪声 混合同余法 FPGA Verilog HDL 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)