基于变换采样的超宽带接收机设计

的增强型PLL或者快速PLL对系统时钟倍频产生采样时钟,采样时钟最大为500 MHz。该系统采用变换采样的原理对UWB脉冲周期信号进行采样,需要在每一个脉冲重复周期内进行(等效采样率的倒数)的延时。延时芯片选用sy8929 7u,该芯片为双通道可编程延时线,每个通道的延时范围为2~7 ns,可编程延时增量为5 ps。延时变化基于串行可编程接口(SCLK,SDATA和SLOAD),每个通道的控制字为10 bit。为了增加延时,可以将多个sy89297u串联起来使用。

2.3 数字硬件

FPGA的并行性处理方式,使得FPGA成为高速ADC芯片高速数据流进行接收、缓存处理的理想方案,同时,这也是整个系统设计的关键。该系统采用芯片XC5VLX30—1FFG676I。该芯片array为,slice为4 800,最大可分配RAM为320 kb,最大高速I/O为400个,特别适合高速率大数据容量的处理。本文脉冲重复频率为1 MHz,AD的采样率为320MHz,那么在一个脉冲重复周期内将有320个采样点,但是由于一个周期内脉冲的占空比较小,为了减小资源的占用,降低数据率,在每个周期内只取那些有脉冲的采样点进行存储。在数据进行存储时,需要将数据进行拼接,然后再顺序进行读取。为了降低数据的速率,还需要对数据进行非相干累加,这样就可以通过外部端口进行输出,在这里我们选用USB端口与PC连接,通过控制上位机,可以在电脑上进行数据的分析。

3 实验结果与分析

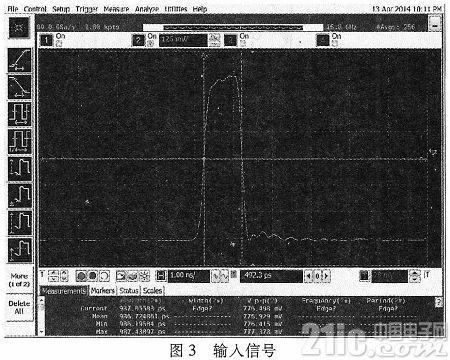

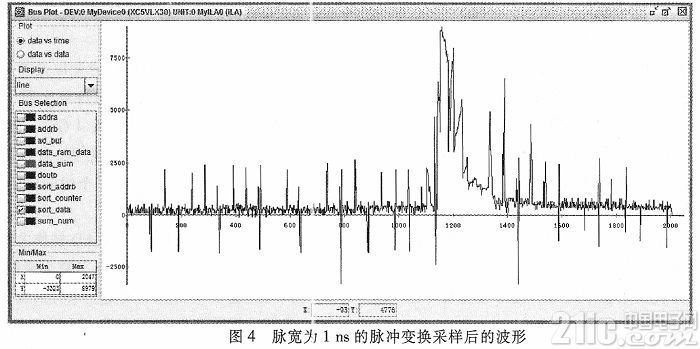

该系统用于无失真接收脉冲超宽带周期信号。超宽带信号脉冲重复频率为1 MHz,脉宽为1 ns,如图3所示。ADC的采样时钟由FPGA内部的增强型PLL对系统时钟倍频产生,而每个脉冲重复周期的采样时钟延时由延时芯片控制,每个周期的延时时间为125 pg。调试采样的采样时钟为320 MHz,而每个脉冲重复周期内只选取40个采样点。采样间隔为1/320μs,那么要恢复一个完整的脉冲需要25个周期。在第一个周期内得到40个采样点,将其存到地址为0,25,50,…,975的非相干累加RAM中,在第二个周期内,我们将采样时钟延时125 ps后得到的采样值存到地址为1,26,51,…,976的RAM中,依次,可以得到25个周期1000个采样点,然后在将这些点从输出缓存RAM中顺序读出,即可得到经过排序的采样数据了。通过Chipscope抓取排序后的信号,如图4所示。当超宽带脉冲脉宽为10 ns时,通过变换采样采出来的波形如图5所示。 Chipscope的观察时钟为320 MHz,而输出缓存RAM的读时钟为160MHz,因此顺序读出的信息数据在时间轴0~2 000内。由于输入噪声的叠加,变换采样的波形带有一定的毛刺。如果在射频变压器之前放置一个低噪放(LNA),那么采样出来的波形将会平滑很多。

4 结论

文中设计了一种基于变换采样的超宽带接收机,其重点集中在脉冲的变换采样部分。脉冲采样主要是通过接收机上的ADS5463芯片实现,而脉冲采样时钟是通过接收机上的FPGA和可编程延时芯片进行控制,数据处理是通过FPGA进行实现。实验结果表明,该接收机能够对上GHz带宽的超宽带信号进行采样接收,等效采样率可以达到8 GS/s。这可以用于超宽带通信与测距。

变换采样 FPGA 可编程延时芯片 ADC UWB 接收机 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)