基于DSP技术的软件锁相环设计

0 引言

随着世界环境污染与经济危机的曰趋严重,可再生能源的研究越来越受人们重视。作为最有开发前景可产生可再生能源的变流器并网技术成为人们研究的重点。其中锁相技术是其核心技术。

常用的锁相有硬件锁相和软件锁相。传统的硬件锁相就是通过逻辑器件对电压信号进行过零检测,电路简单、设计巧妙,但具有一些不足,当电网电压发生频率、相位突变或三相电压不平衡时很难实现锁相,动态性能较差。而软件锁相具有良好的抗干扰能力,能以较高的精度、较快的速度实现锁相。

因此,本文在分析锁相环基本原理的基础上,搭建并网试验平台,采用设计自由、适应性强的软件锁相技术,试验表明,本软锁相技术可很好地实现锁相。

1 锁相环基本原理

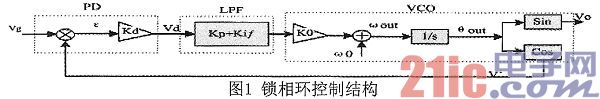

锁相环是一个相位误差反馈系统,由鉴相器(PD)、低通滤波器(LPF)和压控振荡器(VCO)组成,其工作原理是将输入的电压信号与SPLL内部信号的相位差转换为直流量,经过滤波器后通过压控振荡器,实现信号的频率和相位的调整,从而使其与电网电压同频同相,其控制结构图如图1所示。

其中,鉴相器采用乘法器,构成基于乘法鉴相器的闭环锁相环,将压控振荡器的输出信号v0与输入信号vg进行相位比较,从而产生相位差的误差电压vd。

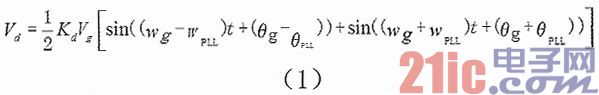

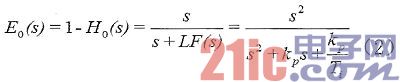

鉴相器输出式(1):

上式中可以发现,鉴相器输出的相位差中存在高频分量,因此需要通过低通滤波器来滤除其中的高频成分。低通滤波器实际上是一个比例积分控制器PI,滤除误差电压vd中的二次谐波分量和噪声,以确保系统的稳定性,通过PI控制器的误差传递函数输出为式(2)。

压控振荡器在锁相环路中起了一次积分的作用,即压控振荡器实际上是锁相环路中的固有积分环节,完成电压/频率的变换。

2 硬件电路设计

2.1 DSP28335简单介绍

本文采用的DSP芯片为TMS320F28335,该芯片具有一个12位带流水线结构的模/数转换器和6个独立的ePWM模块。ADC具有16个通道,1个转换内核,可实现顺序采样和同时采样。一个完整的ePWM输出通道包括EPWMxA和EPWMxB两路信号。实验系统中的IPM模块驱动信号由该模块产生。

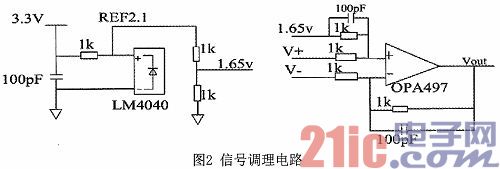

2.2 信号调理电路

本设计采用霍尔电压传感器VSM025对交流电压进行采样,将采集到的电网电压转换成在-3~+3V之间;同时通过信号调理电路对传感器输出的电压信号进行差分放大和抬升,并输出0~3V电压信号,通过DSP的AD采样后进行信号的采集和处理。其信号调理电路如图2所示。

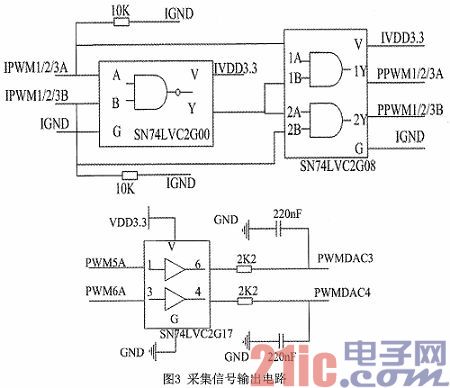

2.3 信号输出电路

PWM信号是一系列可变脉宽的脉冲信号,其输出可以用来表征模拟信号,在PWM输出端进行积分可以得到期望的模拟信号。本系统中产生的PWM波通过逻辑芯片来驱动IPM模块,通过RC低通滤波电路到PWMDAC口将波形输出观察。其电路图如图3所示。

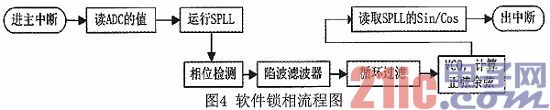

3 软件算法设计

并网发电系统中,通过锁相技术实现电网电压相位的锁定,从而使逆变输出的电流与电网电压同频同相。锁相技术中其控制精度直接影响到并网运行的性能。软件锁相的流程图如图4所示。

4 实验验证

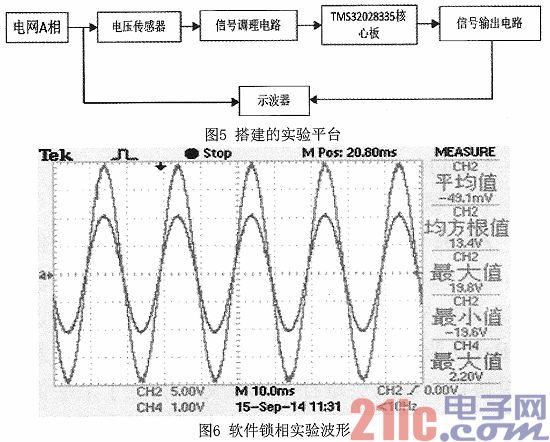

4.1 采用PWMDAC进行验证

为了验证软件锁相的效果搭建了实验平台,该平台包含模拟电网、电压传感器、信号调理电路、DSP(TMS320F28335)核心板、信号输出电路、数字示波器六个部分,如图5所示。

通过霍尔电压传感器检测电网三相电压中一相的电压,将采集到的信号通过信号调理电路进行处理,随后经DSP的AD口进行采样,并在DSP的内部进行锁相,并通过PWM口的RC滤波电路进行输出。通过数字示波器观察PWMDAC口的输出波形与电网电压波形来判断锁相的效果。

示波器观察波形如图6所示,系统中模拟电网的电压为18V,如蓝线(上)所示,绿线(下)为PWMDAC口输出电压。通过观察可以发现,PWMDAC的波形和电网电压相位一致,很好地实现了电网电压相位的锁定。

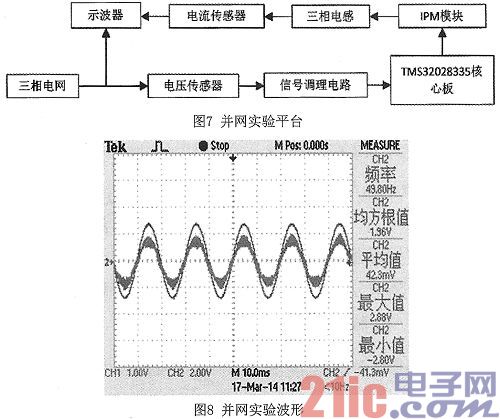

4.2 并网验证

在软件锁相的基础上搭建并网实验平台,包含三相模拟电网、电压传感器、信号调理电路、DSP(TMS320F28335)核心板、IPM模块、三相电感、电流传感器、数字示波器八部分,如图7所示。其中IPM模块使用的是三菱公司的型号为PS21765的模块,IPM内部集成了逻辑、控制、检测和保护电路。三相电感的电感值为7mH。电流传感器检测输出电流信号,其信号调理电路与电压一样。

DSP产生的PWM信号,经过逻辑电路来驱动三菱公司的IPM,并网时,先观察锁相波形及输出电压,在满足条件的前提下实现并网。并网结果波形如图8所示,红线为输出电流波形,蓝线为通过传感器后的电网电压波形。

通过观察发现,并网逆变器的输出电流和电网电压相位一致,从而实现相位锁定和逆变器并网。

5 总结

本文从软件锁相的理论出发,设计实现了基于DSP技术的锁相环,解决了传统硬件锁相精度不高、准确度差的

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)