基于FPGA+DM36X的IP摄像机平台

近年来,随着信息化技术以及物联网的发展,对于视频监控设备的要求不断的在提高,将高动态范围(High Dynamic Range,HDR)摄像机代替传统摄像机以提高监控质量成为了监控设备的发展趋势。TI公司达芬奇视频处理技术在网络摄像机视频监控方面的成功运用,使得DM36X芯片与其他芯片相比具有低功耗、小尺寸、低成本、高性能等特点。但由于高动态摄像机的数据量非常大,同时对图像处理的要求也很高,这就增加了系统的复杂性。要同时满足高质量的视频图像处理效果和实时传输,单凭DM36X的处理能力已远不够,且DM36X内部的视频处理算法已固定,众多优秀的图像处理算法无法及时的添加进去,这也对DM36X图像处理能力的升级造成了一定的困难。而FPGA芯片处理速度快、灵活性高,可根据各种优秀算法进行较好的设计,所以系统选用FPGA进行前端HDR视频图像增强预处理部分,由此可在较大程度上减少DM36X的工作量,弥补其在高动态视频处理上的不足,使DM36X能完全发挥高速编码和传输效的特点,满足系统实时性要求。将FPGA和DM36X共同运用在网络摄像机平台中可充分发挥各自的优势。这种设计不仅使得系统在日后扩充和再次开发上提供了足够的灵活性,且有利于整个系统的升级与维护。

本系统是在TI公司基于达芬奇技术TMD320DM36X处理器的IP Camera方案基础之上搭建基于FPGA+DM36X的IP摄像机平台,采用高动态网络摄像机MT9M034进行图像采集,以FPGA +DM36X作为HDR视频图像增强、编码和传输处理核心,最终完成用户通过远程PC机客户端上观看1 280×720分辨率,每秒30帧的实时视频。

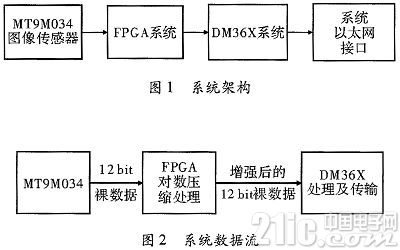

1 总体方案

系统架构如图1所示,MT9M034采集HDR视频信号,FPGA负责对HDR视频图像进行增强处理,DM36X负责对增强后的HDR图像进行编码传输等处理。

系统3部分之间的数据流如图2所示。

图像传感器MT9M034经过配置后输出动态范围为120 dB的HDR图像。图像数据的位宽是20 bit,可选择性的压缩成12 bit或14 bit。由于DM36X处理能力的限制,在本系统中将传感器输出数据位宽设置为12 bit,这就会造成图像数据的损失。所以本方案在原IP Camera的基础之上添加了FPGA系统,可根据需要灵活增加底层的图像处理算法。首先图像传感器输出的视频数据在FPGA上进行捕获和对数压缩等处理,达到对图像增强的效果。然后再将这12位裸数据传输给DM36X系统,并在DM36X系统中完成色彩空间转换、伽马校正、RGB转YUV、边缘增强等一系列处理。最终将处理过的视频图像数据以H.264标准压缩后通过以太网接口传送到TCP/IP网络,完成用户通过远程PC机客户端上实时监控视频。

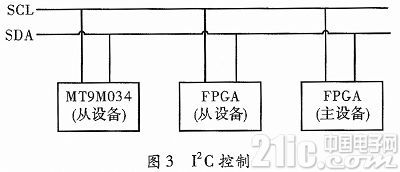

MT9M034(从设备)、FPGA(从设备)、DM36X(主设备)之间通过I2C总线进行通信。DM36X作为主设备不仅可通过I2C总线对MT9M034进行配置,还可对FPGA进行简单控制,如图3所示。

原DM36X IPNC的驱动程序是针对MT9T031传感器设计的。而本系统中采用的图像传感器是MT9M034。MTM034和MT9T031虽均是美光公司推出的图像传感器,寄存器位宽均为16 bit,但其寄存器编址位宽是有差别的,MT9T031传感器的寄存器编址是8 bit,而MT9M034传感器的寄存器编址是16 bit。为了使DM36X能对MT9M034传感器进行配置,需要对DM36X的驱动进行移植。

2 FPGA硬件电路设计

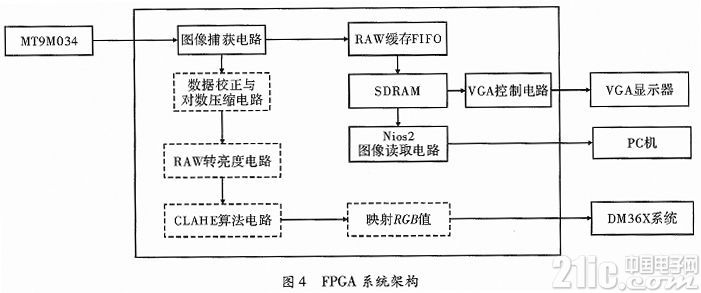

如图4所示,在FPGA上需要设计的电路包括图像捕获电路、数据校正电路、RAW转亮度电路、CLAHE色调映射电路和用于调试图像传感器的VGA显示电路。

DM36X将MT9M034配置好并启动后,图像传感器会输出12 bit的HDR图像数据,这些数据直接进入图像捕获电路模块,此模块主要是对数据进行标记和对行、列、帧等进行计算,为后面的电路设计提供必要的参数。MT9M034图像传感器通过分段性覆盖整个亮度域的3次曝光合成一副20 bit位宽的HDR图像,并将20 bit亮度分三段折线模拟对数压缩到12 bit输出,增加了传感器的实时性。因为普通的显示器只能显示8 bit数据,所以需要色调映射算法将HDR图像压缩成8 bit低动态范围图像(Low Dynamic Range Image,HDRI)这样既可保持图像整体明暗效果,又可使图像的细节部分很好的体现出来。由于传感器内部的三段线性压缩和标准的对数压缩曲线之间具有一定的差距,会使原HDR图像损失许多的细节信息,若直接进行色调映射算法的处理的话会影响图像的对比度,所以在进行色调映射之前需要进行对数据进行校正,最大程度上消除传感器三段线性压缩造成的误差,然后在进行对数压缩这样就可将整个图像的亮度压缩到一个较小的范围内,最后在通过色调映射算法实现图像效果的增强。由于时间原因在FPGA中仅实现图像

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)