深入理解ARM体系架构(S3C6410)---S3C6410系统时钟

时间:11-09

来源:互联网

点击:

2].Otherwise, the IPs on APB bussystem cannot transfer data correctly.

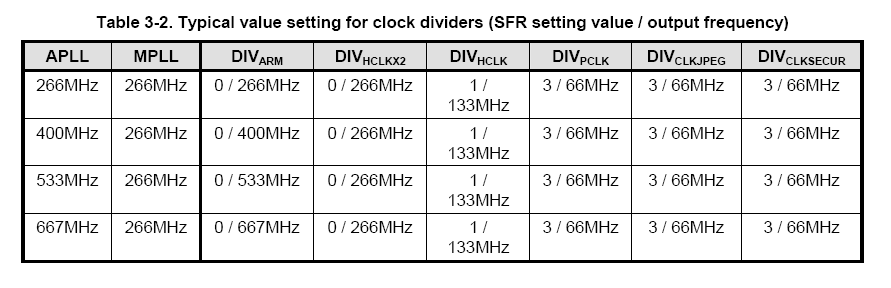

在AHB总线上的JPEG和安全子系统不能运行在133MHz。AHB总线用divjpeg和divsecur为它们单独产生时钟信号,因此它们与APB之间的频率也要隔着一个偶数。

APLL单独用于ARM核,其值不作约束。

其他时钟,用的时候查看手册即可。

2)MFC时钟

3)camera I/F(接口)时钟

4)显示时钟(POST、LCD和scaler

5)音频时钟(IIS和PCM)

6)UART、SPI、MMC时钟

7)IrDA 和USBHOST时钟

8)时钟的开关控制

可以通过控制HCLK_GATE、PCLK_GATE、SCLK_GATE。

9)时钟的输出

有一个时钟输出端口,产生内部时钟,用于中断或调试。

ARM体系架构S3C6410系统时 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)