系统时钟和定时器简单记录

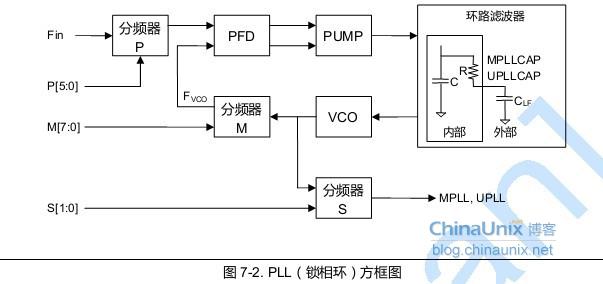

锁相环(PLL):时钟发生器之中作为一个电路的MPLL,参考输入信号的频率和相位同步出一个输出信号。用于生成与输入直流电压成比例的输出频率的压控振荡器(VCO)、用于将输入频率(Fin)按p分频的分频器 P 、用于将VCO输出频率按m分频并输入到相位频率检测器(PFD)中的分频器M用于将VCO输出频率按s分频成为Mpll(输出频率来自MPLL模块)的分频器S、鉴相器、电荷泵以及环路滤波器。

鉴相器(PFD ):PFD检测 Fref 和Fvco之间的相位差,并在检测到相位差时产生一个控制信号(跟踪信号)。Fref 意思为参考频率。

电荷泵(PUMP )

电荷泵将PFD 控制信号转换为一个按比例变化的电压并通过外部滤波器来驱动 VCO。

环路滤波器

PFD产生用于电荷泵的控制信号,在每次 Fvco与Fref 比较时可能产生很大的偏差(纹波)。为了避免 VCO过载,使用低通滤波器采样并且滤除控制信号的高频分量。滤波器是一个典型由一个电阻和一个电容组成的单极性RC滤波器。

压控振荡器(VCO)

从环路滤波器的输出电压驱动 VCO,引起其振荡频率线性增大或减小,如同均匀变化电压的功能。当Fvco与Fref 频率和相位都在限期内相匹配时,PFD 停止发送控制信号给电荷泵,并转变为稳定输入电压给环路滤波器。VCO频率保持恒定,PLL 则保持固定为系统时钟。

PLL和时钟产生器的通常条件 (参见文档)

如何控制锁相环PLL的输出频率呢?MPLLCON(FCLK和Fin的比例关系)和CLKdivN寄存器(FCLK、HCLK和PCLK之间的比例关系):FCLK=(2*m*Fin)/(p*2^s)

m=Mdiv+8,p=Pdiv+2,s=Sdiv。(MPLLCON寄存器中)。注意:在系统初始化阶段应该先初始化UPLL(USB时钟),然后等待大约7个nop指令之后,再初始化MPLL.这也就是启动代码时,需要注意的。同时最好按照官方给出的系统时钟配置参考。

例子:已知系统外部晶振输入为12MHz,要求FCLK输出为200MHz,经过计算可以得到Mdiv=92,Pdiv=4,Sdiv=1。

M_Mdiv EQU 92 //Fin=12.0MHz,Fout=200MHz

M_Pdiv EQU 4

M_Sdiv EQU 1

ldr r0 ,=MPLLCON

ldr r1 ,=((M_Mdiv<12)+(M_Pdiv<4)+M_Sdiv)

str r1,[r0]

下面配置CLKdivN寄存器,实现FCLK、HCLK、PCLK之间的分频比。其中HdivN用于控制FCLK和PCLK的比例关系;PdivN主要用于控制HCLK和PCLK的比例关系。

定时器原理与应用

S3C2440有5个16位定时器,定时器0、1、2、3被称为PWM定时器。定时器 4 是一个无输出引脚的内部定时器。定时器 0 还包含用于大电流驱动的死区发生器。(时钟源是PCLK)

定时器原理相同,寄存器TCMPBn和TCNTBn用于缓存定时器n的比较值和初始化值;TCON用于控制定时亲的开启与关闭;可以通过读取寄存器TCNTOn得到定时器的当前计数值。

TCMPBn的值是用于脉宽调制(PWM)。当递减计数器的值与定时器控制逻辑中的比较寄存器的值相匹配时定时器控制逻辑改变输出电平。因此,比较寄存器决定 PWM 输出的开启时间(或关闭时间)。

定时器工作原理概述:

首先、将定时器的比较值和初始值装入寄存器TCMPBn和TCNTBn中。

然后、设置定时器控制器TCON启动定时器。此时、TCMPBn和TCNTBn中的值会加载到寄存器TCMPn和TCNRn中。

此时、定时器会减1计数,即TCNTn进行减1计数,当TCMPn=TCNTn时,TOUTn引脚输出取反。TCNTn继续减1计数。

当TCNTn的值到达0时,其输出管脚TOUTn再次发转,并触发定时器n的中断。(如果中断使能的话)

当TCNTn的值到达0时,如果在TCON寄存器中将定时器n设置为“自动取反”,则自动加载初值,下一轮计数流程开始。

可以通过读取TCNTOn读取观察定时器当前的值。PCLK经过两级分频器,输出频率作为定时器的工作频率。

定时器配置寄存器TCFG0用于控制第1级分频器的分频系数,分频器输出频率为:

PCLK/(prescaler value+1),其中prescaler value=0~255.

定时器配置寄存器TCFG1用于控制多路开关。

定时器的输入时钟=PCLK/(prescaler value+1)/(divider value)

prescaler value=0~255;divider value=2、4、8、16

例子:设置适当的分频系数,使定时器0的输入时钟为62.5kHz

假如PCLK为50MHz,则50MHz/62.5kHz=800,可以是第一级分频系数为100,第2级的分频系数为8即可满足要求。

rTCFG0 &= ~(0xFF);

rTCFG0 |=99;

rTCFG1 &=~(0xf);

rTCFG1 |=0x02;

总体思路是

系统时钟定时 相关文章:

- 整理系统时钟定时器--SysTick的应用(11-26)

- 系统时钟和定时器;MPLL和定时器(11-24)

- STM32 SysTick 系统时钟 超简易定时器SysTick(11-13)

- 系统时钟和定时器——PWM定时器(11-11)

- 系统时钟和定时器——看门狗定时器(11-11)

- 浅谈STM32F10X芯片SysTick系统时钟定时器(11-11)