基于DSP技术的通用型数字变频器系统设计

在上述三个计算公式的基础上,我们可以得出该变频器数字控制的整个流程:从霍尔电流传感器输出的Ui=2.5±△V,此电压先后施加到由TLC2274构成的两个减法电路上,第一路以Ui减去传感器采样结果的中值参考电压2.5V,然后再线性放大到A/D采样所要求的电压范围。第二路则相反,再中值参考电压Uref减去传感器输出电压Ui,同样也线性放大到合适的电压范围。在变频器数字控制系统的设计中,Z1、Z2为两个3.3V的稳压二极管,对运放输出电压起到限幅作用。当Ui值>Uref时,则Uo1输出为正电压,且电压范围是0-3.3V,而由于二极管D2的存在使得电流不能注入到运放中,故而第二路运放不能输出负电压,而是钳位在0V。当Ui值

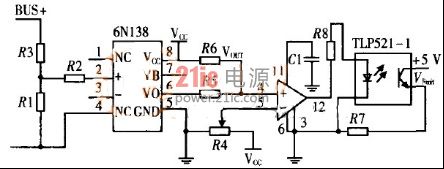

在进行这一通用型数字变频器的系统设计过程中,还有一个问题需要我们特别注意,那就是由于电机启动时的电流非常大或因控制回路、驱动电路等误动作,会造成输出电路短路等故障,因此需要一种能快速检测出过大电流的电路。这里我们主要采用2SD315A自身检测和检测直流母线的双重检测以及在故障发生时,采用软、硬件同时封锁的方法。为有效地保护功率IGBT和直流滤波电容,在该系统中我们还设计了母线电压过欠压保护电路,故障检测原理如图4所示。图4中,6N138为一个线性光电隔离器,输出电压信号与母线电压成正比,当通过光电隔离器件后,可以直接供给DSP控制系统进行采样。同时,将输出Vlimit信号送至DSP,触发中断保护。

图4 故障检测原理图

系统控制算法软件实现

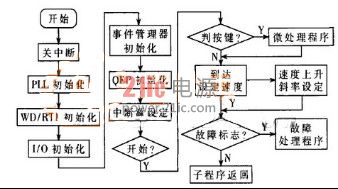

基于DSP技术的数字控制是本方案中的设计重点,该种数字控制系统主程序图如下图图5所示。在本方案中的算法设计中,主程序模块主要功能是完成系统的初始化,PLL时钟的设定:DSP工作频率设为20MHz。输入输出端口初始化。事件管理器初始化。定时器1、2、3的设定、全比较PWM单元设定、死区单元设定。QEP工作方式设定。中断管理初始化:中断除复位、NMI位,只允许PDPINT、中断3。PDPINT是功率设备保护中断,中断3用于系统完成控制算法。

图5 数字控制系统主程序图

以上就是本文所介绍的一种基于DSP技术的通用型数字控制变频器系统设计方案,希望能够对各位工程师的日常研发和设计工作有所帮助。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)