分布式异构处理的行业应用

引言

通过按钮与消费电子产品进行互动的时代已经过去。人机交互在过去几年中发生了巨大变化并仍不断发展。本文将提供人机界面变化的一些实例,帮助读者更充分地了解如何使用一种特别的架构实现低功耗解决方案,提升电池供电应用的用户体验。该架构由基于低功耗FPGA实现的异构处理单元实现。

人机界面(HMI)发展趋势

大多数移动设备在被唤醒进入工作之前都会进入睡眠或低功耗模式,所以您与设备的第一次交互操作即是唤醒。这种“唤醒”可以通过手腕翻转、摇动、单击或双击、来电或消息、机械按钮按压以及特定短语、手势或声音(例如拍手或打响指)触发。每种“唤醒”方法都需要使用传感器和监测装置来侦测特定的动作。“唤醒”操作必须以极低的功耗实现。 现在的低功耗 FPGA 能够以大约 100uW 的功耗实现实时在线、实时聆听解决方案,而未来功耗还能显著降低。

实现创新的 HMI 解决方案所需的各种传感器正在迅速改变 I/O 发展的格局。现在的移动设备需要更高的 I/O 速率。在过去几年中,低成本传感器的激增以及全新的更高性能接口的广泛采用增加了这类系统的计算需求。而对实时在线功能的需求也在不断增长——传感器在无人机、电话、可穿戴设备和工业设备等各种应用中持续收集大量数据。系统设计工程师需要在加快数据处理的同时降低系统功耗,在不再次充电的情况下满足消费者一整天的设备使用需求。

移动系统设计需要一种更全面并基于系统的解决方案,而不是以 CPU 为中心的传统设计方法。系统设计工程师需要充分利用处理器的差异性来尽可能降低功耗,与此同时满足当今移动设备日益增长的计算需求。

欢迎来到分布式异构处理(Distributed Heterogeneous Processing, DHP)的时代

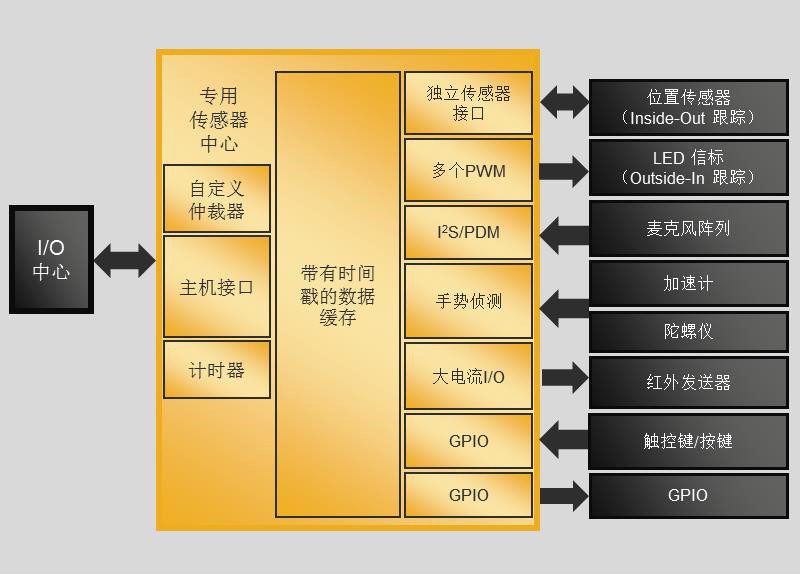

DHP 是一种全新的低功耗解决方案,使用本地算法而不是云端算法,使用不同的处理器而不是功耗很高的应用处理器(AP)。通过这种设计,设计工程师可以使用并行处理技术满足复杂协处理的新需求,使用本地数字信号处理器(DSP)执行重复的数据处理任务, 降低功耗并使应用处理器不再参与某些处理任务,从而使其能够长时间地处于睡眠模式以节省系统功耗和延长电池使用时间。

分布式异构处理——本地处理可降低功耗并加速响应

更多存储空间、更多 DSP

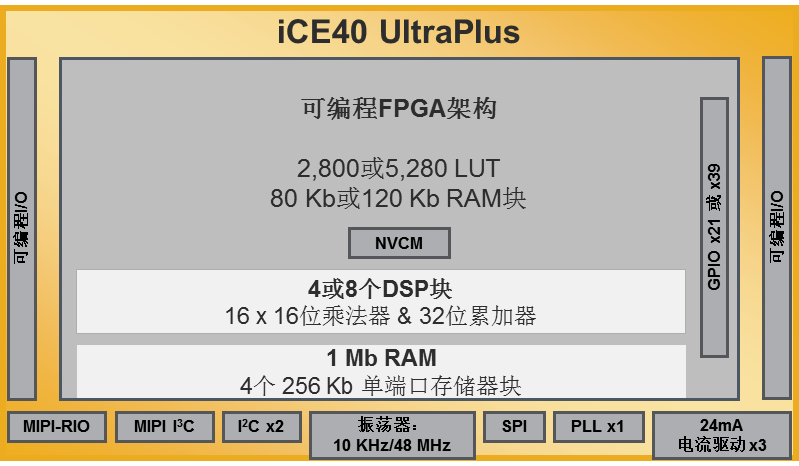

莱迪思半导体公司为 iCE40 Ultra FPGA 产品系列添加了新成员,可满足对于 DHP 计算需求,帮助设计工程师实现功耗更低的解决方案,相比上一代产品具备 8 倍的存储空间和 2 倍的 DSP。全新的iCE40 UltraPlus FPGA 拥有更多逻辑资源,静态电流仍仅需 75μA,而上代产品的静态电流为 71μA。

iCE40 UltraPlus FPGA 提供多种封装尺寸,使得设计工程师能够为当今竞争激烈的移动市场快速构建独一无二并且极具吸引力的解决方案,满足下一代消费电子、移动、物联网边缘和工业产品的严苛处理需求。

该全新的 FPGA 属于低功耗 iCE40 产品线。iCE40 Ultra系列结合了低功耗和高度集成的功能等特性,包括多个 16 x 16 位乘法器块以及超小的封装尺寸。

全新 iCE40 UltraPlus FPGA 为用于重复数字处理的低功耗并行处理解决方案提供所需的全部关键资源。1.1 Mbit 低功耗 SP-SRAM、8 个乘法器/累加器块用于信号处理,高达 5280 LUT 用于用户逻辑,以及用于瞬时启动应用的非易失性配置存储器,iCE40 UltraPlus 解决方案为设计工程师实现实时传感器缓存、声束形成音频子系统和其他重复计算密集型应用 提供了理想的蓝图。该器件也可以用于支持各种桥接、缓存和显示应用,助力加速下一代 移动和工业应用的创新。

莱迪思 iCE40 UltraPlus FPGA 框图

全新的 iCE40 UltraPlus FPGA 还添加了可提供设计灵活性的可编程 I/O、支持始终在线摄像头应用的 I3C 接口(由 MIPI 定义的全新高带宽数据和控制传感器接口)以及内置振荡器,能够降低功耗和 BOM成本。

功能丰富的 iCE40 UltraPlus FPGA 静态功耗低至 75μA,封装尺寸小至 2.15 x 2.55 mm,适用于要求功耗极孝空间受限的消费电子类应用。该器件还提供 QFN 封装,支持工业和其他消费电子类应用使用的低成本 PCB 组装。

- 分布式PLD解决方案可降低服务器成本并提升灵活性(09-05)

- 莱迪思推出业界功耗最低的语音侦测和识别解决方案(03-23)

- 全新的CROSSLINK解决方案应用实例(03-01)

- 莱迪思等宣布推出新款基于FPGA的图像传感器解决方案(12-05)

- 莱迪思推出全球首款通过USB Type-C接口,同时支持4K60fps视频和USB 3.1数据的superMHL解决方案(08-04)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)