使用QDR-IV设计高性能网络系统——第三部分

时间:02-22

来源:电子产品世界

点击:

个 ECC校验位)传输到ECC逻辑内。因此,ECC逻辑会提供已纠正的36位输出数据。

无ECC位的QDR/DDR SRAM的SER故障率(FIT)通常为200 FIT/Mb。但带有ECC时,该数值将为0.01 FIT/Mb,提高了4个数量级。

QDR-IV存储器控制器的设计建议

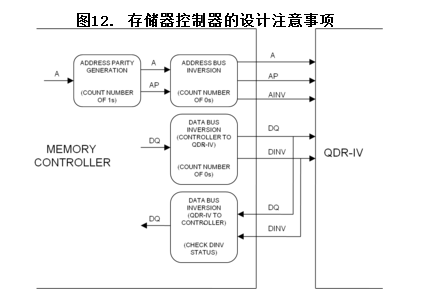

本节提供一些存储器控制器启用QDR-IV的地址奇偶校验和总线翻转功能的设计建议。

存储器控制器首先要根据地址总线生成地址奇偶。然后,需要在地址总线和地址奇偶位上进行地址翻转。

对于数据总线转换,将数据发送给QDR-IV前,存储器控制器需要计算每个DQ总线上的逻辑“0”的数量,以便生成相应的DINV位(取决于数据总线翻转条件)。

将数据发送给存储器控制器时,QDR-IV使用相同的数据总线翻转逻辑。为了识别QDR-IV的接收数据,控制器仅要检查相应DINV位的状态。如果控制器接收DINV = 1,需要翻转相关的数据总线;否则,保持接收到的数据位不变。

图12显示的是存储器控制器的设计注意事项。

- 基于QDR-IV SRAM 实现网络流量管理统计计数器 IP设计(09-07)

- 使用QDR-IV设计高性能网络系统——第二部分(02-22)

- 使用QDR-IV设计高性能网络系统——第一部分(02-22)

- 基于DSP的广播级数字音频延时器(06-07)

- 脱机视频图象编/解码系统中高速DSP芯片应用方案(07-28)

- 一种基于CAN总线与以太网的嵌入式网关经典设计(09-10)