基于DSP的软件锁相环的实现

0 引言

准确获取电网基波及谐波电压的相位角,在变频器、有源滤波器等电力电子装置中具有重要的意义,通常需要采用锁相环得以实现。传统锁相环电路一般由鉴相器、环路滤波器、压控振荡器及分频器组成,其工作原理是通过鉴相器将电网电压和控制系统内部同步信号的相位差转变成电压信号,经环路滤波器滤波后控制压控振荡器,从而改变系统内部同步信号的频率和相位,使之与电网电压一致。传统锁相环存在硬件电路复杂、易受环境干扰及锁相精度不高等问题,随着大规模集成电路及数字信号处理器的发展,通过采用高速DSP 等可编程器件,将锁相环的主要功能通过软件编程来实现。本文设计的锁相环控制系统采用数字处理器TMS320F2812 芯片实现对电网基波及特定次谐波电压相位的跟踪和锁定。

1 软件锁相环的设计方案

1.1 工作流程

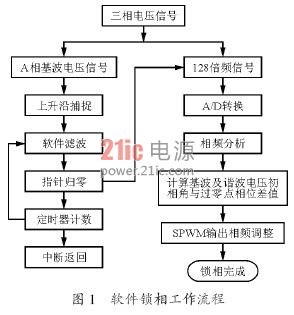

基于DSP的软件锁相环设计此方案的基本思路是通过采样电压过零点获取同步信号,采用DSP 内部定时器的循环计数产生同步信号来实现压控振荡器和分频器的功能,即通过改变定时器的周期或最大循环计数值的方法来改变同步信号的频率和相位,同时对电压进行A/D 转换及数据处理,得出基波及谐波电压的相位与频率,调整SPWM 正弦表格指针地址完成对基波及谐波电压的锁相功能,其工作流程如图1 所示。

通常,过零信号可以通过检测电网三相电压中任一相的过零点获取。在图1 中,以检测A相电压过零点作为过零信号,将通过上升沿捕捉及软件滤波后产生的中断作为采样周期同步信号,当DSP内部时钟倍频后产生的中断在捕获到输入电压信号在过零点时,将发正弦信号的指针归零,以保证输入电压信号过零时DSP发出的基准正弦信号也同步过零,从而实现相位同步。本文采用SPWM 触发模式,基准正弦信号是一个正弦数据表格,控制逆变器输出的基准点;同时采样电压信号,经DSP进行FFT计算分析其相位和频率、基波及谐波与A相电压过零点相位差,通过修改定时器周期寄存器来改变SPWM 输出时正弦波的频率;以修改比较寄存器来改变SPWM 输出时正弦波的相位,这样完成了对基波及谐波电压的相位锁定。

1.2 过零检测电路的设计

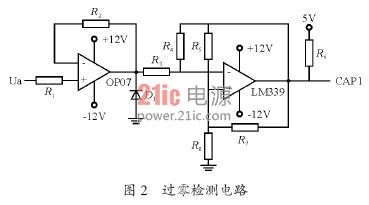

过零信号对系统相位捕捉的精准性影响较大,系统设计时采用软硬件结合的办法实现对过零信号的捕捉。获取过零信号实质上是为了给系统提供一个同步信号,即每次信号过零时启动A/D转换。在本设计中,过零检测电路采集A相电压每个周期的过零点作为系统产生的中断信号CAP1,使中断服务程序开始执行,图2 为电压信号过零检测电路。

图2 中,在比较器芯片LM339 的输出端选择加装了上拉电阻,主要是考虑到整个电路对驱动、功耗和速度的要求。电阻R7和R8构成一个滞回比较器,输出信号通过反馈电阻R7 改变同相端的参考电压,以消除输入信号正反过零产生的抖动。

1.3 过零捕捉的软件实现

过零检测主要解决的是采样同步问题,当检测到的电压信号由负到正过零时,比较器芯片LM339 输出端产生上升沿,将此信号输入到DSP2812 事件管理器EVA 的引脚CAP1。引脚CAP1 在系统初始化程序中预设置为上升沿触发中断,因此当过零信号到来时,CAP1中断子程序开始执行,开启事件管理器EVA 的TIMER 周期中断,周期设置为驻T/128 s(每周期采样128 个点),触发A/D 模块采样。其中,驻T 为CAP1 捕捉到的两个过零检测信号上升沿的间隔时间,等于电网待测信号的周期T,图3 为过零中断程序的流程。

DSP 的捕获单元CAP隶属于事件管理器,它能够捕捉到CAP 外部引脚的跳变,当捕捉到对应引脚发生特定的跳变时,触发相应的中断,并将定时器的值存入一个两级深的FIFO堆栈中。本方案设计每16 点启动一次数据分析,同时投出一次控制量,这个过程为一个更新周期,判断标志ctrl 用来检测是否进入新的更新周期,以判断是否需要启动新一轮数据分析和投出控制量。标志位dft用来判断当前数据分析状态,为0 时表示重新初始化数据分析操作,为1 时表示数据分析操作完毕,为2 时表示允许启动新一轮数据分析,为3 时表示当前正在进行数据分析。图4 给出了捕获单元的软件流程。

1.4 过零信号的软件滤波

CAP1 捕捉到的两个过零信号上升沿的间隔时间,即两个CAP1中断事件的间隔时间,等于电网待测信号的周期T。TIMER 在系统初始化后不断计数,然后在CAP1 的中断服务程

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)