基于FPGA的高速数据采集卡设计与实现

引言

数 据 采 集 系 统 是 信 号 与 信 息 处 理 系 统 的 重 要 组 成 部 分,随着信息技术和高速互联技术的飞速发展,人们面临的 信号处理任务越来越繁重,数字信号处理的速度和精度也越 来越高,高速数据采集卡的重要性日益凸显。要解决高分辨 率、高精度等问题,对存储设备的读写速度、高速ADC技 术指标的要求必然会提高。FPGA灵活的配置与验证设计方 法、丰富的IP核资源,大大简化了DDR II SDRAM读写和以 太网MAC协议层的设计,给设计带来了便利。

1 高速数据采集卡总体方案

系统以FPGA器件为核心,DDR II SDRAM为存储设备,14-bit高精度ADC为核心模数转换芯片,使用以太网技术作 为数据传输协议,设计了高速数据采集卡解决方案。数据采集卡的核心控制芯片是Xilinx公司的Virtex-5系列 的FPGA,主要完成整个采集卡的配置、存储设备以及以太网的接口,触发逻辑和测频逻辑设计。高速数据采集卡最高

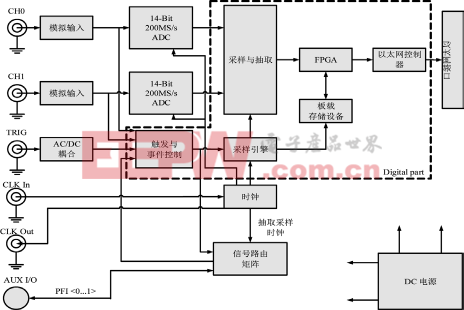

图1 系统整体结构图

设计采样率可达到212.5MSPS,采样精度12-bit,具有高输入范围、512MB深存储容量等特性,具有多种触发模式、频率 检测等功能。

高速采集卡系统的面板上总共有6个接插件, 分别为 CH0、CH1、TRIG、CLK In、CLK Out、AUX I/O。CH0和 CH1是两路模拟输入接口,TRIG是外部触发接口,CLK In 和CLK Out是外部输入时钟和输出参考时钟的接口,AUX用 于软件测试阶段配置信息传输。

系统大致分为如下几个模块:两路模拟通道、触发模 块、时钟模块、电源模块、数据获取模块、抽取模块、板载 存储模块、以太网接口、信号输入输出模块和板载存储模块 等。其中数据获取模块、抽取模块、信号输入输出模块、部 分存储模块和部分以太网接口等多个功能模块在FPGA内部 通过可编程逻辑门阵列实现,系统结构如图1所示。

系统硬件设计中各功能模块的主要功能为:

1、两路模拟通道 该模块主要指从双通道模拟信号的输入到ADC模数转

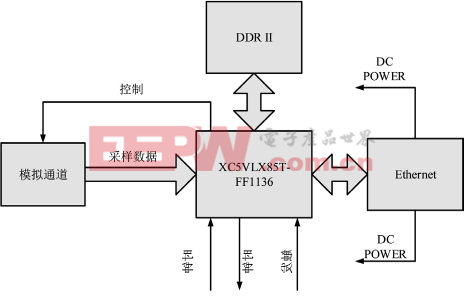

图2 FPGA数字电路原理框图

换器的部分,由于存在多种满量程输入范围和垂直偏置,因 此输入的模拟信号需要经过模拟调制,调制过程包括输入阻 抗的匹配、耦合方式、放大衰减、原始信号调零与垂直偏置 等。通过一系列的电路调制,最终在进入ADC之前将多种 模拟满量程基本统一到同一个电压等级上。由于项目要求12-bit分辨率,并考虑设计余量,所选的ADC应大于12-bit分 辨率。

图3 嵌入式逻辑分析仪抓取ADC通道1信号波形

图4 DDR II SDRAM读操作仿真图

2、触发模块 触发模块实现外部触发和通道触发,可通过编程实现

触发源的切换。外部输入的触发信号可经过DAC和比较器电 路经过比较产生。通道触发可通过模拟输入经过调制之后进 入ADC之前的信号引入比较,产生触发信号。

3、时钟模块

时钟模块主要需要设计板载时钟电路和FPG A时钟电 路, 选择合适的VCXO作为时钟源, 与外部输入时钟经过 PLL和时钟分发产生合适的时钟用于ADC采样和FPGA对数 字信号的获取。

4、电源模块 电源模块分为模拟电源部分和数字电源部分,多数电源芯片供应商对FPGA及其外围电路电源设计都有推荐电源 模块及设计指导,模拟电源部分要考虑一颗电源芯片带动多 个芯片工作,驱动电流和功耗都是设计中需要注意的问题。

5、板载存储模块 设计要求单通道512MB的存储深度,由存储深度及数据流的传输速度,考虑使用双倍数据率的SDRAM实现,两

路模拟通道共需1GB的存储量,至少需要1GB的存储单元。

2 FPGA数字逻辑设计

FPGA的设计主要包括各芯片控制模块、DDR II SDRAM 存储接口设计、以太网数据传输接口设计、触发控制设计和 测频计数逻辑设计五部分。整个FPGA数字电路原理框图如 图2。A D C 是 系 统 采 样 的 核 心 器 件 , 选 用 A D I 公 司 生 产 的

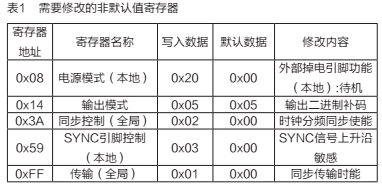

A D 9 6 4 3 , 它 是 一 款 双 通 道 、 1 4 位 、 采 样 速 率 最 高 达 2 5 0MSPS的模数转换器,使用三线SPI协议来配置寄存器。每 行存储器映射寄存器表有8-bit空间。存储器映射分为三部 分:芯片配置寄存器(地址0x00~0x02)、通道索引和传输 寄存器(0x05、0xFF)、ADC功能寄存器,包括设置、控制 和 测 试 ( 地 址0x08~0x59)。 表 1 列 出 了 需 要 手 动 修 改 的 非 默 认 值 寄 存 器 及 修 改值 。 其 他 寄 存器 都 保 持 默 认配置不变。

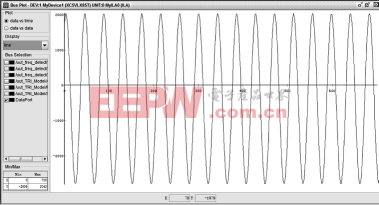

通过嵌入式逻辑分析仪Chipscope验证ADC配置的正确 性,输入的测试信号为600mVpp的周期性正弦模拟信号,频 率为5MHz,经过通道1调理到±1V电压范围后,进入ADC 前加入-40mV的直流偏置。

使用嵌入式逻辑分析仪抓取信号如图3。经过计算可知 进入ADC前的模拟信号为523mVpp,并加入了-40mV的直流 偏置。换算成14-bit数字量分别为4890和-370,而根据逻辑分 析仪抓取的信号Max=2045,Min=-2806计算可得对应的数字 量分别为4850和-380,误差范围达到了设计要求。

存储器控制器状态机使用的初始化顺序遵循 DDR I I SDRAM 标准规范。接口需符合存储器的电压要求。因此在 经过固定步骤的初始化后,控制器进入空闲模式,等待读写 操作。如图4是DDR II SDRAM存储设备控制器的读操作的仿 真实现。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)