理解并满足FPGA电源要求(上)

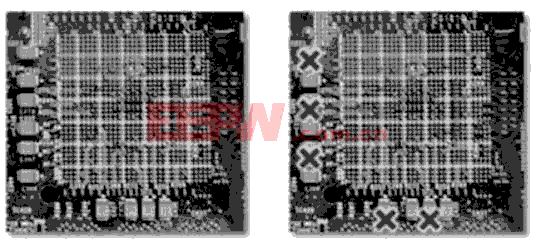

图1 使用Enpirion PowerSoC解决方案

在 C y c l o n e V S o C 开 发 套 件 上 采 用 E n p i r i o n PowerSoC解决方案替代现有的供电电源解决方 案,供电电源引脚布局减小了22% (1a),功耗降 低了35% (1b),去掉了昂贵的钽电容,所需的体 电容减少了一半,从而减小了体积,降低了成本 (1c)。

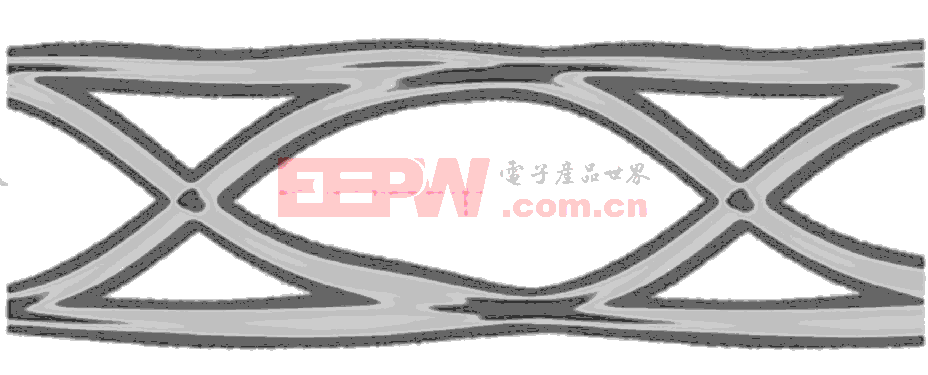

图2 眼图

Stratix V GX FPGA电路板上11.3 Gbps信号的眼图。使用了一片EN6337QI Enpirion

PowerSoC,将VCCRT_GXB和VCCA_GXB收发器引脚的VIN = 3.3 V转换为VOUT

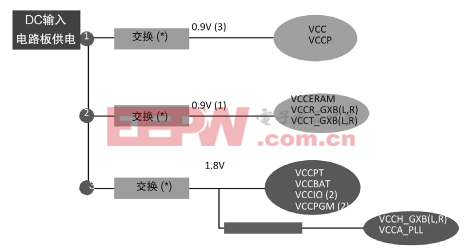

图3 为Arria 10 GX推荐的电源树

实现高密度布板,减小了杂散电感和电容。其次,较高的开 关频率还支持更宽的控制环带宽,也就意味着转换器能够更

迅速的响应负载变化,结合使用更小的体电容,工作时也就

很少出现上冲或者下冲。由于体电容通常体积较大而且价格 昂贵,因此,减少体电容不但提高了瞬时响应以保证无缝 工作,而且还节省了大量的电路板面积,降低了成本。图1 说明了这一优点,一个Altera Cyclone? V SoC设计使用了独立的开关调节器,而相同的设计采用了Enpirion? PowerSoC。 Enpirion PowerSoC设计工作在较高的开关频率下,利用独特 的磁体和封装集成技术,使用了很少的电感和电容,实现了 密度极高的引脚布局,因此,器件的波纹很低,瞬时响应很 快。用在Cyclone V SoC设计中,Enpirion PowerSoC将供电电 源引脚布局减小了22%,功耗降低了35%,不再需要5个较大 而且昂贵的钽电容,体电容数量减少了一半。

在Cyclone V SoC开发套件上采用Enpirion PowerSoC解决方 案替代现有的供电电源解决方案,供电电源引脚布局减小了

22% (1a),功耗降低了35% (1b),去掉了昂贵的钽电容,所需 的体电容减少了一半,从而减小了体积,降低了成本(1c)。

4 噪声敏感输入

虽然逻辑是FPGA架构的主要构件模块,而FPG A还实现了很多其他的模块,例如,锁相环(PLL),用在FPGA内部,将参考输入时钟与反 馈时钟的上升沿对齐,

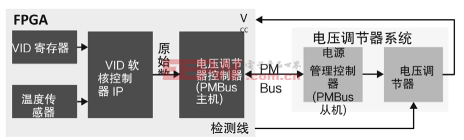

图4 SmartVID实现

还有高速收发器,这是很多网络、通信、存储和其他 电子系统中不可或缺的组成。这些电路模块对供电电源噪声 非常敏感,因为噪声会导致产生抖动,随之带来很高的误码 率(BER),降低了电路性能。FPGA及其最终应用要求的边 沿速率越来越高,使得越来越难以维持信号完整性。

结果,需要特殊考虑FPGA中这些模块的供电电源,以减小电源轨噪声。有时候,如果敏感的电源轨与系统中的另一稳压电源轨有相同的电压要求,可以使用铁氧体磁珠等价格便宜的小滤波器。但是,在很多情况下,要求使用输出噪声非常低的电源转换器,才能获得合适的稳定的电压。传统 上,FPGA电路板设计人员简单的使用低泄漏输出线性调节 器(LDO),这通常会有较高的供电电源抑制比(PSRR),理论 上,不会产生开关噪声。然而,线性调节器的效率非常低, 随着收发器功耗需求的增长,系统总功耗预算越来越受限, 浪费的功率以及额外产生的热量导致带来更大的系统难题。 为解决这些难题, 敏感的FPG A电源轨可以使用很多 Enpirion PowerSoC解决方案,因为这些解决方案经过设计, 实现了LDO的噪声性能,同时维持了开关调节器的高效特 性。如图2Stratix V GX FPGA电路板上高速信号张得很开的眼 图所示,这是因为采用了Enpirion PowerSoC为收发器电源轨 供电。高频硅片设计,即使是高频工作时也能够减小开关损 耗的高效的开关FET技术,以及减小了杂散电感的独特的封 装结构,正是这些因素相结合,实现了低噪声性能。(未完待续)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)