基于国产龙芯GS32I的小系统的硬件设计

图3 存储系统的硬件设计示意图

⑴ FLASH接口设计及相关寄存器的设计

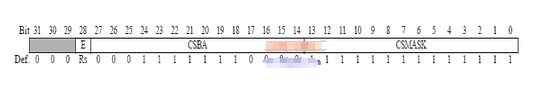

28F320C3 FLASH的存储容量为2M×16 bit。由于SRAM/Flash EPROM控制器设置为32位总线宽度,使用两片28F320C3 FLASH扩展为32位总线宽度,地址线连接至GS32I地址总线的RAD2~RAD22,每次读取四个字节; GS32I复位后起始地址是 0x0 1FC0 0000,FLASH的地址被装载到此处,每个片选信号的地址映射范围是通过设置片选地址寄存器mem_staddr0来实现的,片选地址寄存器 mem_staddr0的格式如下所示:

当E位置为1并且满足条件“(physical_addr&CSMASK)==CSBA”时,片选信号将变为有效。 physical_addr是内部系统总线作为输出的实际的36位物理地址,CSBA用来指定这个片选信号的物理基地址的31:18位,CMASK用来指定CSBA的哪些位被用来译码片选信号。CSBA的高四位,也就是35:32位由mem_stcfg0寄存器的DTY域来决定。本系统中,mem_stcfg0寄存器的DTY域设置为3,则对应的高四位35:32位的值为0000B,CSBA设置为0x07F0,CMASK设置为 0x3FF0这样FLASH的地址就被映射到0x0 1FC0 0000—0x0 1FFF FFFF。

FLASH最快读取速度为70ns, CPU系统总线周期为10ns(100MHz),因此在读取FLASH时需要插入等待状态,通过设置静态时序寄存器mem_sttime0来插入等待周期。静态时序寄存器mem_sttime0的格式为:

Ta域为数据有效时片选信号要求插入的周期数,考虑到系统的稳定性,根据FLASH的读取参数,插入7个等待周期,因此Ta域设置为7。Ta域默认值为29,在选取启动ROM芯片时,若芯片读取参数需要插入的等待周期超过29,则这种芯片不可用。Tcsh域用来指定在两次访问期间片选信号保持的时钟周期数,这里设置为0。

⑵ SRAM接口设计及相关寄存器的设计

SRAM的存储容量设计为512K×32位,可使用两片IS61LV51216 SRAM(512K×16)通过位扩展实现。将RCS1#连接到SRAM的片选信号CS#上,地址线连接至GS32I地址总线的RAD2~RAD20,地址范围是通过设置片选地址寄存器mem_staddr1来映射的,设置方法与mem_staddr0的实现相同。

SRAM时序与CPU的配合是通过设置静态时序寄存器mem_sttime1来完成的,mem_sttime1的格式与的mem_sttime0相同。IS61LV51216 SRAM的读写速度最快为10ns, 片选信号RCS1#插入一个等待周期,Ta域设置为1,Tcsh域设置为0。对于SRAM的写入,与其相关的域有Twcs,用来指定写脉冲RWE#后片选信号RCS1#保持的时钟周期数, Tcsw用来指定片选信号RCS1#有效后的几个时钟周期插入RWE#,Twp用来指定RWE#持续的时钟周期数。根据SRAM的参数和SRAM的读写时序,本设计中,Twcs,Twp都设置为0,Tcsw设置为0000b,这样使SRAM与CPU的时序能够配合且保证系统的稳定性。设置完成后,SRAM 的读写时序如下图所示:

图4 SRAM读写时序图

4.其他外部设备的设计

GS32I处理器提供48个GPIO口,其中22个专用,48个GPIO中的32个由主GPIO块控制,另外16个是次级GPIO口。每个GPIO 口可以被配置作为输入或输出,并且能够连接到内部中断控制器对输入的信号产生一个中断。本设计中采用GPIO管脚作为外设的数据信号和控制信号。

- 基于DSP的广播级数字音频延时器(06-07)

- 脱机视频图象编/解码系统中高速DSP芯片应用方案(07-28)

- 一种基于CAN总线与以太网的嵌入式网关经典设计(09-10)

- 在异步SRAM中实现速度与功耗的完美平衡(01-03)

- 针对微控制器应用的FPGA实现(06-06)

- 数字图像倍焦系统设计与实现综合实例之:系统原理框图(06-05)