数字图像倍焦系统设计与实现综合实例之:系统原理框图

时间:06-05

来源:互联网

点击:

12.3系统原理框图

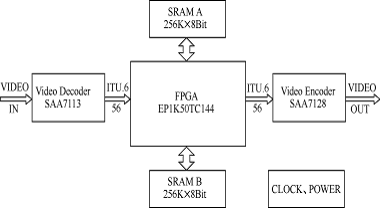

本系统采用了两片SRAM存储器构成乒乓缓冲结构来完成视频的采集和处理,视频的采集和输出部分采用了应用广泛的SAA71XX系列。

数字图像倍焦系统的原理框图如图12.3所示。

图12.3数字倍焦系统原理框图

系统框图各部分模块介绍如下

(1)VideoDecoder模块。

视频输入是PAL格式的,利用VideoDecoder芯片可以将PAL格式的模拟视频信号转换成ITU656格式的数字视频信号。ITU656信号就可以直接送入FPGA进行采集和处理了。

(2)VideoEncoder模块。

视频输出是PAL格式的,利用VideoEncoder芯片可以将ITU656格式的数字视频信号转换成PAL格式的模拟视频信号。

(3)FPGA模块。

FPGA是系统的核心部分,完成所有数字信号的处理功能,包括图像的采集、倍焦放大以及输出等。本系统采用了Altera公司的ACEX1K系列的EP1K50芯片。

(4)SRAM模块。

SRAM作为系统的缓冲区来完成图像的暂存功能。SRAM需要缓存行变换后的结果,每场图像尺寸为720´288,行变换后为720´192=138240,近似为139KB。因此,用一片256KB的SRAM就可以缓存一场行变换结果。

(5)CLOCK、POWER模块。

CLKOCK模块给系统提供时钟电路,采用晶体振荡器来实现。POWER模块为系统提供电源。系统输入为5V,POWER模块可以将输入的5V信号转换为3.3V和2.5V电源。

下面来详细介绍FPGA的内部结构设计。

数字图像倍焦系统 SRAM存储器 乒乓缓冲 FPGA 相关文章:

- 数字图像倍焦系统设计与实现综合实例之:FPGA内部结构设计(06-05)

- 数字图像倍焦系统设计与实现综合实例之:系统硬件配置方案(06-05)

- 数字图像倍焦系统设计与实现综合实例之:系统工作原理分析(06-05)

- 数字图像倍焦系统设计与实现综合实例之:设计需求分析与芯片选型(06-05)

- 数字图像倍焦系统设计与实现综合实例之:FPGA在其他视频和图像处理系统中的应用(06-04)