数字图像倍焦系统设计与实现综合实例之:系统工作原理分析

12.2 系统工作原理分析

如前所述,本系统主要完成对输入视频图像的两倍放大。图像的放大主要是通过插值算法来实现的,下面详细分析如何应用双线性插值算法来实现倍焦功能。

1.符号约定

首先对系统工作原理分析中用到的符号做一个约定:

表示像素点坐标,在本系统中

表示像素点坐标,在本系统中 。

。

表示原始图像,其宽度为

表示原始图像,其宽度为 ,高度为

,高度为 。

。

表示倍焦后图像,其宽度为

表示倍焦后图像,其宽度为 ,高度为

,高度为 。

。

通过双线性插值完成数字倍焦功能,即将原始图像插值为原来2倍大小,仍然以原来的分辨率输出,即 ´x

´x 。

。

2.双线性插值原理描述

对新图像中每一点为 ,在本系统中

,在本系统中 ,查找其在原图像中的相邻位置

,查找其在原图像中的相邻位置 。

。

点的灰度值

点的灰度值 的计算公式为(12-1)。

的计算公式为(12-1)。

(12.1)

(12.1)

公式(12-1)中需要计算的数值为 ,如公式(12-2)~(12-5)所示。

,如公式(12-2)~(12-5)所示。

(12.2)

(12.2)

(12.3)

(12.3)

(12.4)

(12.4)

(12.5)

(12.5)

3.硬件实现的简化

为减少硬件计算的复杂性,对 的算法做如下处理。

的算法做如下处理。

(1)硬件乘法器是必须的,用以完成 和

和 的计算,但由于:

的计算,但由于:

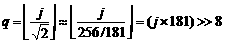

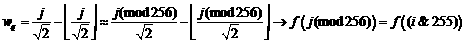

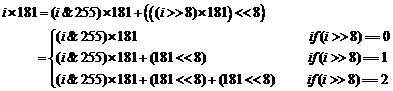

所以可以考虑只用8bit´8bit硬件乘法器(而不是16bit´8bit硬件乘法器),即如公式(12-6)所示。

公式(12-6)

公式(12-6)

(2)求权重 的公式已经写成关于

的公式已经写成关于 、

、 的函数的形式,该函数可以通过离线计算并存储一张表格(“权重表”)的方法实现。该表的大小为256´8bit。注意求

的函数的形式,该函数可以通过离线计算并存储一张表格(“权重表”)的方法实现。该表的大小为256´8bit。注意求 查询的是同样的表格。

查询的是同样的表格。

4.算法优化

(1)乘法器设计的简化。

在 的计算过程中,需要一个常数乘法器(´181),通过查表完成。而

的计算过程中,需要一个常数乘法器(´181),通过查表完成。而 也需要查表,查表也需要一个周期来完成。如果用同一个表,那么

也需要查表,查表也需要一个周期来完成。如果用同一个表,那么 需要串行查出,速度太慢。如果要同时查出来,需要多个表,片内存储器太大。

需要串行查出,速度太慢。如果要同时查出来,需要多个表,片内存储器太大。

因此,在计算过程中需要使用移位和加法进行配合,来提高运算速度。

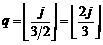

基于这个考虑,将放到2倍的条件放宽到2.25倍,即用1.5´1.5来替代1.414´1.414。这样,公式(12-2)~(12-5)就简化为公式(12-7)~(12-10)的形式。

公式(12-7)

公式(12-7)

公式(12-8)

公式(12-8)

公式(12-9)

公式(12-9)

公式(12-10)

公式(12-10)

这样, 不必查表产生,而是1/3和2/3交替。关于除3的操作,可以通过一个256´8bit的查找表来完成。

不必查表产生,而是1/3和2/3交替。关于除3的操作,可以通过一个256´8bit的查找表来完成。

需要说明的是,经过上面的调整,放大的倍数为2.25倍,而不是2倍。

(2)行列的处理顺序的优化。

原算法中水平和垂直方向同时插值,需要4个像素类计算。但是,实际硬件实现过程中如果读取4个数据来计算一个像素点,那么输出很难保证连续,而且速度太慢。因此,实现过程中,对整场图像先做行插值,再做列插值。即将二维线性插值转为两个一维线性插值,如公式(12-11)所示。

公式(12-11)

公式(12-11)

其中 依次取1/3和2/3。这样每次插值操作只与两个像素值有关,一个是前一个像素(寄存器中),另一个是当前读出的像素。

依次取1/3和2/3。这样每次插值操作只与两个像素值有关,一个是前一个像素(寄存器中),另一个是当前读出的像素。

当接收原始帧时,在裁剪后写入SRAM过程中完成行插值;从SRAM读出过程完成列插值,并输出。

考虑到视频信号是按行扫描的,而且是隔行扫描,因此处理过程以场为单位。

(3)硬件实现简化前后的结果对比。

从图12.1和12.2的对比图中可以看出,放大2.25倍的图像视野上要比放大2倍的图像小一些,但是图像质量并没有明显降低。

图12.1 放大2倍后的图像 图12.2 放大2.25倍后的图像

- 数字图像倍焦系统设计与实现综合实例之:FPGA内部结构设计(06-05)

- 数字图像倍焦系统设计与实现综合实例之:系统硬件配置方案(06-05)

- 数字图像倍焦系统设计与实现综合实例之:系统原理框图(06-05)

- 数字图像倍焦系统设计与实现综合实例之:设计需求分析与芯片选型(06-05)

- 数字图像倍焦系统设计与实现综合实例之:FPGA在其他视频和图像处理系统中的应用(06-04)

- FPGA与DSP协同处理系统设计之:典型实例-FPGA片上硬件乘法器的使用(06-05)